### University of Central Florida

## **STARS**

Electronic Theses and Dissertations, 2020-

2022

# MoS2 based Memristive Synapses for Neuromorphic Computing

Adithi Pandrahal Krishnaprasad Sharada *University of Central Florida*

Find similar works at: https://stars.library.ucf.edu/etd2020 University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2020- by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Krishnaprasad Sharada, Adithi Pandrahal, "MoS2 based Memristive Synapses for Neuromorphic Computing" (2022). *Electronic Theses and Dissertations, 2020-.* 1239. https://stars.library.ucf.edu/etd2020/1239

#### MOS<sub>2</sub> BASED MEMRISTIVE SYNAPSES FOR NEUROMORPHIC COMPUTING

by

#### ADITHI PANDRAHAL KRISHNAPRASAD SHARADA

B.E. Visvesvaraya Technological University, 2015M.S. University of Central Florida, 2018

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering in the College of Engineering & Computer Science at the University of Central Florida

Orlando, Florida

Summer Term 2022

Major Professor: Tania Roy

$\ \odot$  2022 Adithi Pandrahal Krishna<br/>prasad Sharada

#### **ABSTRACT**

Brain inspired computing enabled by memristors have gained prominence over the years due to its nano-scale footprint, reduced complexity for implementing synapses and neurons. Several demonstrations show two-dimensional (2D) materials as a promising platform for realization of robust and energy-efficient memristive synapses. Ideally, a synapse should exhibit low cycle-to-cycle (C-C) and device-to-device (D-D) variability along with high maximum /minimum conductance ( $G_{max}/G_{min}$ ) ratio, linearity and symmetry in weight update for obtaining high learning accuracy in neural networks (NNs). However, the demonstration of neuromorphic circuits using conventional materials systems has been limited by high C-C and D-D variability and non-linearity in the weight updates. In this study, we have realized robust memristive synapses using 2D molybdenum disulfide (MoS<sub>2</sub>) to address the concerns like high variability and nonlinear weight update and asymmetry. We have utilized engineering techniques like electrode and stack engineering to realize ultra-low variability and linear weight update in MoS<sub>2</sub> synapses. The ultra-low C-C and D-D variability in SET voltage, RESET power and weight update is demonstrated in Au/MoS<sub>2</sub>/Ti/Au synapses. Further, these synapses were integrated with MoS<sub>2</sub> leaky-integrate and fire (LIF) neurons to realize AND, OR and NOT logic gates proving the viability of these synapses for in-memory computing. However, these MoS<sub>2</sub> synapses suffer from low G<sub>max</sub>/G<sub>min</sub> ratio. We have employed stack engineering to increase G<sub>max</sub>/G<sub>min</sub> ratio while preserving low variability. In that regard, the active medium is modified to a heterogenous stack of MoS<sub>2</sub>/SiO<sub>x</sub> with Ti/Au bottom and top electrodes. We observe an increase in the G<sub>max</sub>/G<sub>min</sub> ratio from 2 to ~10. Further, electrode engineering is used to realize graphene/MoS<sub>2</sub>/SiO<sub>x</sub>/Ni to obtain linear weight update with identical pulses essential for online training of NNs. This work substantiates the necessity of engineering techniques to implement essential synaptic characteristics like ultra-low variability and linear and symmetric weight update.

To my uncle, dad and mom

#### ACKNOWLEDGMENT

"A journey of thousand miles begins with a single step". My arduous and fulfilling journey of achieving PhD in electrical engineering has been filled with many failures and glimpses of wonderful successes. This was possible due to unwavering faith of many people and their unending support. So, this would be a great opportunity to extend my gratitude for their patience and care.

Words wouldn't suffice to describe and thank my advisor Dr. Tania Roy for her unwavering trust and support which always encouraged me to work better. She has been my champion, my mentor and a great friend who applauded my success and appreciated my efforts during the times of failures. This helped me to be a better version of myself both in my career and life goals.

I would like to thank Dr. Vikram J. Kapoor, Dr. Yeonwoong Jung, Dr. Kristopher Olan Davis and Dr. Jiann-Shiun Yuan for being on my committee and for their valuable insights in my research.

I would like to thank my past and present colleagues Hirokjyoti Kalita, Dr. Sonali Das, Dr. Durjoy Dev, Molla Manjurul Islam, Ricardo Martinez Martinez, Dr. Nitin Choudhary, Victor Rodriguez, Madison Manley, Anya Lenox, Victor Okonkwo, Haley Heldmyer and Karl Mama for their support throughout my doctoral research.

I am grateful for all my collaborators in UCF for their support in all our collaborative projects- Dr. Mashiyat Sumaiya Shawkat, Dr. SangSub Han, Dr. Jeya Prakash Ganesan, Dr. Jinho Park, Dr. Emmanuel Okogbue and Dr. Changhyeon Yoo. My heartfelt regards to Dr. Ellen H. Kang (UCF), Dr. Parag Banerjee (UCF), Dr Hee-Suk Chung (Korea Basic Science Institute) and Dr. Mario Lanza (KAUST) for the successful collaborations. This would be a great opportunity to

thank Nathan Aultman, James Ross, Maria Real-Robert, Ernie Gemeinhart, Sandra Griggs and Diana Poulalion for all administrative and technical support.

I would also like to acknowledge the support of funding agencies- National Science Foundation (Grant: NSF-EECS-1845331), Air Force Office of Scientific Research (Award no: FA8651-20-1-0008) and BAE systems (Award no: 1020180) for this work.

This work would not have been possible if it wasn't for the support of my friends- Vyshakh, Kishan, Shruthi, Maithreyi, Prapti, Shahbaz, Nandakishore, Aishwarya and Archana. Thanks for listening to my unending stories about devices and research while prompting me to be on track for obtaining my PhD.

My heartfelt thanks to my family who always appreciated my effort and my hard work and encouraged me to work better every day. The sacrifices made by my father always made me aspire for higher ambitions among which PhD was the first one. This PhD would not have been possible without the support of my uncle Kantha Reddy and aunt Sumithra who have always been my greatest champions. I cannot forget the suggestions and perspectives bestowed by my brother Dr Akshay during the course of this PhD which helped me to have a positive outlook and kept me in high spirits. And thanks to my cousins Swathi, Spurthy and Shreyas for the laughs, encouragement, appreciation, patience and support.

Finally, my gratitude and thanks to Lord Sri Krishna for bestowing the good fortune to meet great people and opportunities which always kept me on track.

## **TABLE OF CONTENTS**

| LIST OF FIGURESx                           | iv  |

|--------------------------------------------|-----|

| LIST OF ACRONYMS (or) ABBREVIATIONSxx      | iv  |

| CHAPTER 1 INTRODUCTION                     | . 1 |

| 1.1 Introduction to 2D materials           | . 3 |

| 1.2 Characteristics of artificial synapses | . 7 |

| 1.2.1 Power consumption                    | . 7 |

| 1.2.2 Device dimensions                    | . 7 |

| 1.2.3 Dynamic range                        | . 8 |

| 1.2.4 Weight update precision              | . 8 |

| 1.2.5 Non linearity factor (NLF)           | . 9 |

| 1.2.6 D-D variability                      | 10  |

| 1.2.7 C-C variability                      | 10  |

| 1.2.8 Endurance                            | 11  |

| 1.2.9 Retention                            | 11  |

| 1.3 Objectives                             | 12  |

| 1.4 Dissertation Overview                  | 13  |

| CHAPTER 2 TYPES OF ARTIFICIAL SYNAPSES     | 15  |

| 2.1 Resistive memory                       | 15  |

| 2.1.1 2D Materials as electrodes in RRAM                  | 15 |

|-----------------------------------------------------------|----|

| 2.1.2 Insulating 2D materials RRAM                        | 17 |

| 2.1.3 Semiconducting 2D materials (active layer) RRAM     | 18 |

| 2.2 Phase change memory                                   | 19 |

| 2.3 Switching mechanisms                                  | 20 |

| CHAPTER 3 PROOF-OF-CONCEPT DEVICE                         | 22 |

| 3.1 Introduction                                          | 22 |

| 3.2 Device schematic                                      | 22 |

| 3.3 Material Characterization                             | 23 |

| 3.4 Electrical Characterization                           | 25 |

| 3.4.1 DC characterization                                 | 25 |

| 3.4.2 Retention Measurements                              | 27 |

| 3.4.3 DC Endurance                                        | 28 |

| 3.4.4 Pulsed I-V measurements                             | 29 |

| 3.5 Conclusion                                            | 34 |

| CHAPTER 4 ULTRA-LOW VARIABILITY MoS <sub>2</sub> SYNAPSES | 35 |

| 4.1 Introduction                                          | 35 |

| 4.2 Device schematic                                      | 35 |

| 4.3 DC characterization                                   | 36 |

| 4.3.1 I-V cycling experiments                                     | 36             |

|-------------------------------------------------------------------|----------------|

| 4.3.2 Endurance 3                                                 | 37             |

| 4.3.3 Necessity of MoS <sub>2</sub> layer for resistive switching | 38             |

| 4.3.4 Role of Ti (top electrode) in resistive switching           | 39             |

| 4.3.5 C-C variability in SET voltage and RESET Power distribution | 40             |

| 4.3.6 D-D variability in SET voltage and RESET Power distribution | 41             |

| 4.4 Mechanism                                                     | 14             |

| 4.4.1 Area dependent resistance scaling                           | 14             |

| 4.4.2 Temperature dependent I-V measurements                      | <del>1</del> 6 |

| 4.5 Synaptic Characteristics                                      | 52             |

| 4.5.1 DC potentiation and depression                              | 52             |

| 4.5.2 Retention                                                   | 53             |

| 4.5.3 Pulsed measurements                                         | 53             |

| 4.6 Conclusion5                                                   | 55             |

| CHAPTER 5 MATERIAL CHARACTERIZATION 5                             | 57             |

| 5.1 Introduction                                                  | 57             |

| 5.2 TEM characterization                                          | 57             |

| 5.2.1 TEM and EDS                                                 | 57             |

| 5.2.2 TEM and EELS characterization                               | 58             |

| 5.3 XPS Characterization                                 | 60 |

|----------------------------------------------------------|----|

| 5.4 Conclusion                                           | 61 |

| CHAPTER 6 LOGIC GATE IMPLEMENTATION                      | 63 |

| 6.1 Introduction                                         | 63 |

| 6.2 Ti/Au/MoS <sub>2</sub> /Ti/Au synapses retention     | 64 |

| 6.3 AND gate                                             | 65 |

| 6.4 OR gate                                              | 66 |

| 6.5 NOT gate                                             | 67 |

| 6.6 Conclusion                                           | 68 |

| CHAPTER 7 STACK ENGINEERING in MoS <sub>2</sub> SYNAPSES | 69 |

| 7.1 Introduction                                         | 69 |

| 7.2 Device schematic                                     | 69 |

| 7.3 Device Characterization                              | 70 |

| 7.3.1 DC characterization and mechanism                  | 70 |

| 7.3.2 SET voltage and RESET power distribution           | 72 |

| 7.3.3 Synaptic measurements                              | 73 |

| 7.4 Conclusion                                           | 75 |

| CHAPTER 8 LINEAR UPDATE MoS <sub>2</sub> SYNAPSES        | 76 |

| 8.1 Introduction                                         | 76 |

|   | 8.2  | Device schematic                                                                                         | 76  |

|---|------|----------------------------------------------------------------------------------------------------------|-----|

|   | 8.3  | Material characterization                                                                                | 77  |

|   | 8.4  | DC characterization                                                                                      | 78  |

|   | 8.4  | 4.1 Comparison between CVD and exfoliated MoS <sub>2</sub>                                               | 78  |

|   | 8.4  | 4.2 Role of SiO <sub>x</sub>                                                                             | 79  |

|   | 8.4  | 4.3 Electrode engineering                                                                                | 80  |

|   | 8.5  | Synaptic Characteristics                                                                                 | 83  |

|   | 8    | 5.1 DC potentiation and depression                                                                       | 83  |

|   | 8.3  | 5.2 Retention and linear weight update                                                                   | 84  |

|   | 8.6  | Mechanism                                                                                                | 89  |

|   | 8.0  | 6.1 Area-dependent resistance scaling                                                                    | 89  |

|   | 8.0  | 6.2 Temperature dependent I-V measurements                                                               | 89  |

|   | 8.7  | Integration of grapheneMoS <sub>2</sub> /SiO <sub>x</sub> /Ni synapses with MoS <sub>2</sub> LIF neurons | 92  |

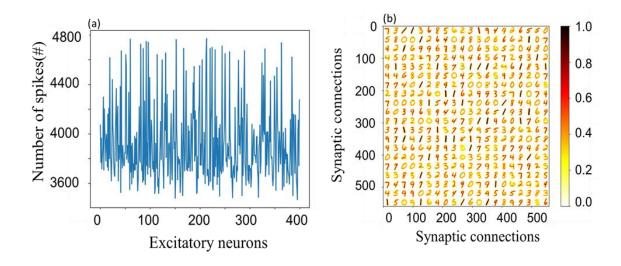

|   | 8.8  | SNN simulation                                                                                           | 94  |

|   | 8.9  | Conclusion                                                                                               | 95  |

| C | CHAP | TER 9 SUMMARY AND FUTURE PERSPECTIVES                                                                    | 97  |

|   | 9.1  | Summary                                                                                                  | 97  |

|   | 9.2  | Future Perspectives                                                                                      | 98  |

| ٨ | DDEN | JDIY: PIGHTS AND PERMISSIONS                                                                             | 100 |

| LIST OF REFERENCES | 104 |

|--------------------|-----|

|--------------------|-----|

## LIST OF FIGURES

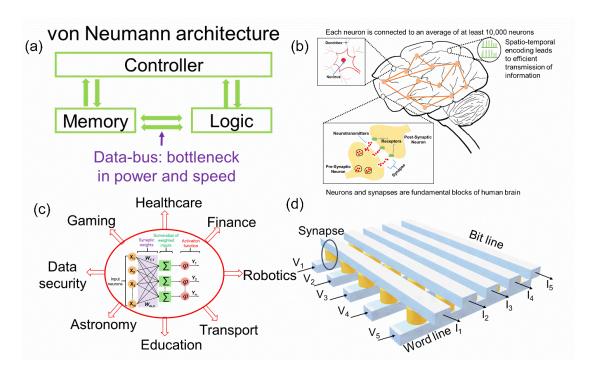

| Figure 1: (a): Schematic showing the conventional von Neumann architecture where the memory                            |

|------------------------------------------------------------------------------------------------------------------------|

| and logic units are physically separated. (b): Paradigm shift in the computing architectures for                       |

| artificial intelligence applications, inspired by the parallel computing observed in human brain.                      |

| (c): NN schematic and artificial intelligence applications. (d): Cross-bar array architecture for                      |

| implementing NNs with a synaptic device (analog memory) at each cross-point                                            |

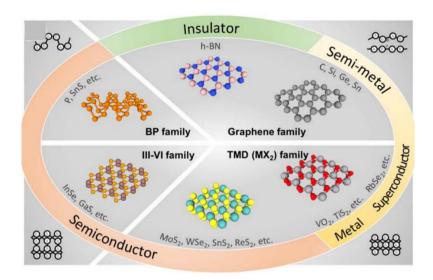

| Figure 2: 2D materials family. Reprinted with permission from the reference [7] © 2018 IEEE 4                          |

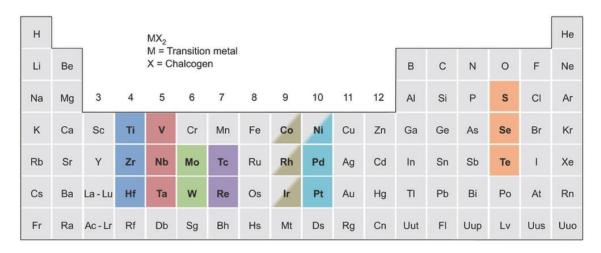

| Figure 3: Periodic table showing various possible TMDCs where the highlighted sections represent                       |

| metal and chalcogen atoms. Reprinted with permission from the reference [14] © 2013 Springer                           |

| Nature                                                                                                                 |

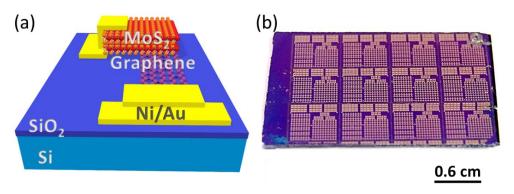

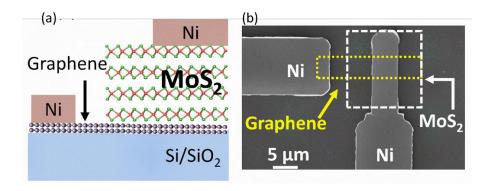

| Figure 4: (a) MoS <sub>2</sub> /graphene device schematic (not to scale) (b) Optical image of fabricated chip          |

| with MoS <sub>2</sub> /graphene memristors                                                                             |

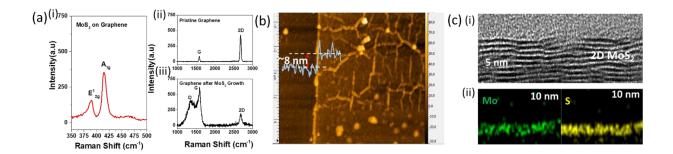

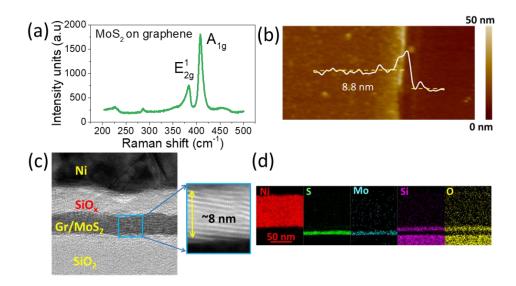

| Figure 5: (a) Raman spectra of (i) CVD-grown MoS <sub>2</sub> on graphene, (ii) pristine graphene, and (iii)           |

| graphene after the growth of MoS <sub>2</sub> . (b) AFM height profile of MoS <sub>2</sub> on graphene, indicating the |

| thickness of MoS <sub>2</sub> to be ~8 nm. (c) (i) Cross-sectional HRTEM image of MoS <sub>2</sub> atomic layers       |

| grown on graphene. (ii) EDS-STEM elemental mapping image of MoS <sub>2</sub> on graphene                               |

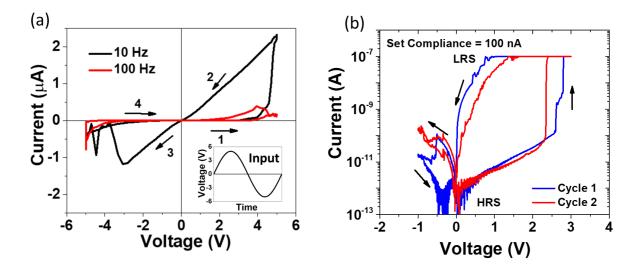

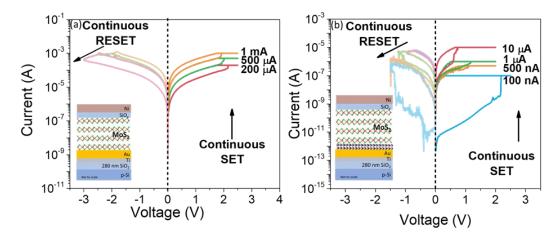

| Figure 6: (a) Pinched hysteresis loop in I-V for sinusoidally varying input voltage of amplitude 5                     |

| V peak-to-peak, and frequency of 10 Hz and 100 Hz, confirming memristive behavior of the                               |

| MoS <sub>2</sub> /graphene device. (Inset: The input waveform) (b) Non-linear IV characteristics of                    |

| MoS <sub>2</sub> /graphene memristors at 100 nA current compliance showing that a high electroforming                  |

| wiosz graphene mennistors at 100 m/r current comphanice showing that a mgh electroforming                              |

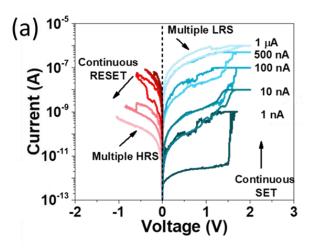

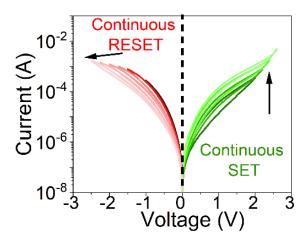

| Figure 7: DC potentiation and depression with continuous SET at 1 nA, 10 nA, 100 nA, 500 nA,                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and 1 µA, followed by continuous RESET using negative reset stop voltages with increasing                                                                                                                                                                                                    |

| magnitude from -0.2 V to -1 V.                                                                                                                                                                                                                                                               |

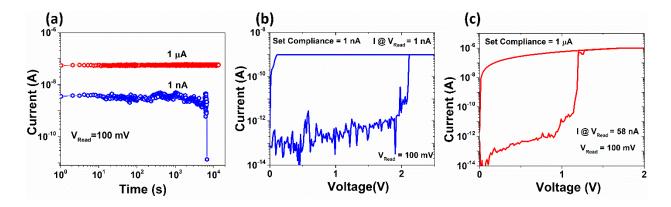

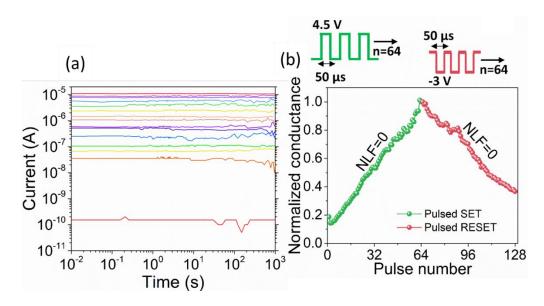

| Figure 8: (a) Data retention of MoS <sub>2</sub> /graphene memristors at 1 nA and 1 µA current compliances                                                                                                                                                                                   |

| for 10 <sup>4</sup> s. (b) Set characteristics of MoS <sub>2</sub> /graphene memristor at 1 nA current compliance for                                                                                                                                                                        |

| retention. (c) The SET characteristics of MoS <sub>2</sub> /graphene memristors at 1 µA current compliance                                                                                                                                                                                   |

| prior to applying pulses (100 mV, 5 ms) for data retention measurements                                                                                                                                                                                                                      |

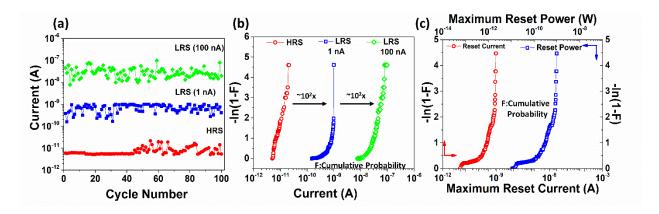

| Figure 9: Endurance characteristics of MoS <sub>2</sub> /graphene memristor. (a) Evolution of HRS and multi-                                                                                                                                                                                 |

| level LRS at 1 nA and 100 nA for 100 DC cycles at $V_{Read} = 2$ V. The SET voltages for 1 nA and                                                                                                                                                                                            |

| 100 nA current compliances are 3.5 V and 4.5 V respectively. (b) Logarithmic distribution of the                                                                                                                                                                                             |

| 2 LRS's and HRS at $V_{Read} = 2 V$ . (c) Logarithmic distribution of maximum reset current and power                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                              |

| for LRS of 1 nA                                                                                                                                                                                                                                                                              |

| for LRS of 1 nA                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                              |

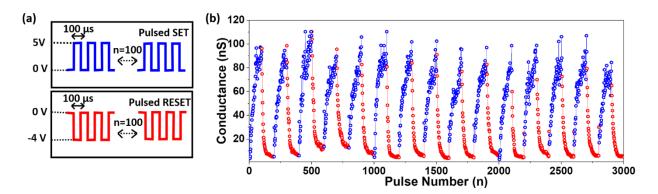

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical                                                                                                                                                                                               |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in                                                                                                  |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in MoS <sub>2</sub> /graphene synapse with the application of symmetric voltage pulses shown in (a) |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in MoS <sub>2</sub> /graphene synapse with the application of symmetric voltage pulses shown in (a) |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in MoS <sub>2</sub> /graphene synapse with the application of symmetric voltage pulses shown in (a) |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in MoS <sub>2</sub> /graphene synapse with the application of symmetric voltage pulses shown in (a) |

| Figure 10: (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in MoS <sub>2</sub> /graphene synapse with the application of symmetric voltage pulses shown in (a) |

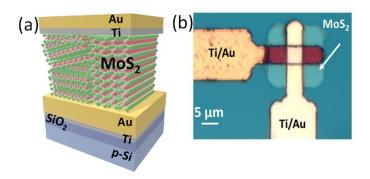

| Figure 13: (a) Device schematic of ultra-low variability memristive synapse. (b) Optical                     |

|--------------------------------------------------------------------------------------------------------------|

| microscope image of the Ti/Au/MoS <sub>2</sub> /Ti/Au device                                                 |

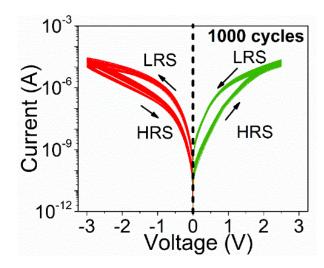

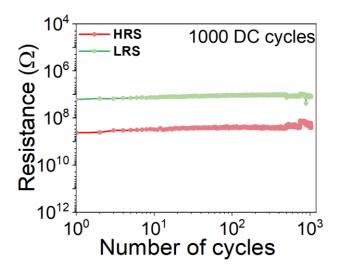

| Figure 14: DC cycling: 1000 cycles indicating the low C-C variability and endurance of MoS <sub>2</sub>      |

| devices                                                                                                      |

| Figure 15: DC endurance of MoS <sub>2</sub> device extracted for 1000 DC cycles. The OFF and ON state        |

| resistance of the device were extracted at 0.25 V to investigate the OFF and ON state variation.             |

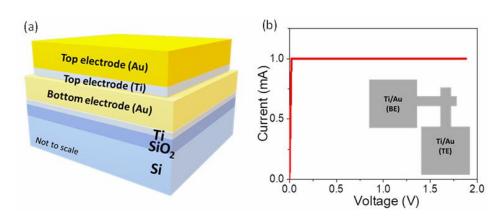

| Figure 16: (a) Schematic of test structure with Ti/Au/Ti/Au. (b) I-V characteristics showing a short         |

| between the top and bottom electrode, indicating that MoS <sub>2</sub> is required for resistive switching.  |

| Inset: Layout schematic of the structure                                                                     |

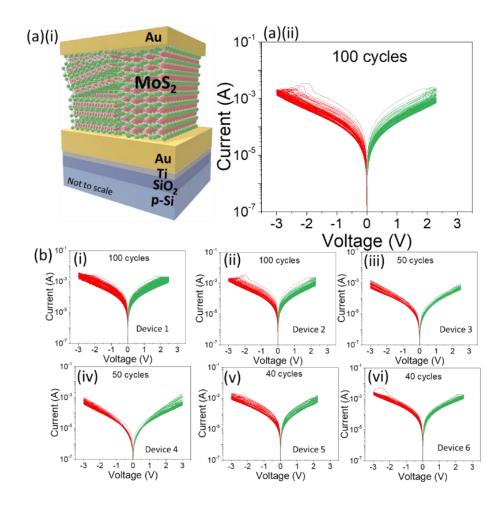

| Figure 17: (a)(i) Ti/Au/MoS <sub>2</sub> /Au (bottom to top) device schematic. (ii) DC characteristics of    |

| Ti/Au/MoS <sub>2</sub> /Au device for 100 DC cycles showing high C-C variability. (b)(i-vi) DC               |

| characteristics of 6 Ti/Au/MoS <sub>2</sub> /Au device exhibiting high C-C variability indicating that Ti is |

| necessary for obtaining low C-C variability                                                                  |

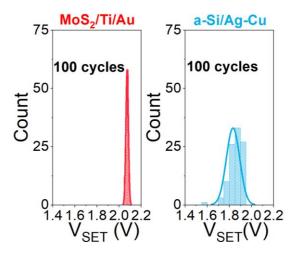

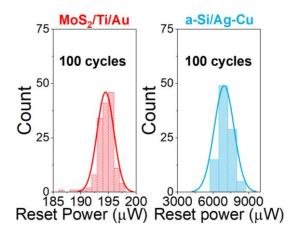

| Figure 18: SET voltage comparison of (i) MoS <sub>2</sub> /Ti/Au and (ii) a-Si/Ag-Cu based device where      |

| MoS <sub>2</sub> device exhibits a tight distribution of 0.04 V for 100 cycles                               |

| Figure 19: RESET power distribution of (i) MoS <sub>2</sub> /Ti/Au device and (ii) a-Si/Ag-Cu device 41      |

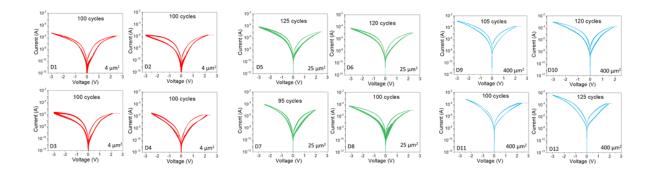

| Figure 20:Individual DC characteristics of MoS <sub>2</sub> devices for >100 cycles from which the SET       |

| voltage and RESET power distribution is extracted to evaluate the D-D variability                            |

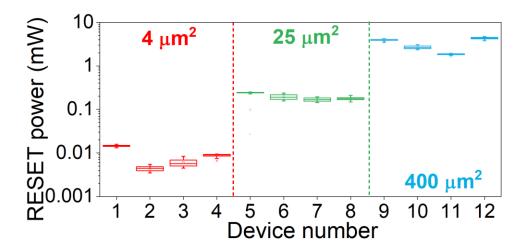

| Figure 21: SET voltage distribution observed in 12 MoS <sub>2</sub> /Ti/Au devices for >100 cycles 42        |

| Figure 22: RESET power distribution observed in 12 MoS <sub>2</sub> /Ti/Au devices for >100 cycles 43        |

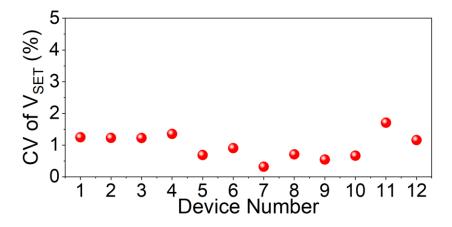

| Figure 23: Coefficient of variation (CV) in the SET voltages in MoS <sub>2</sub> based devices               |

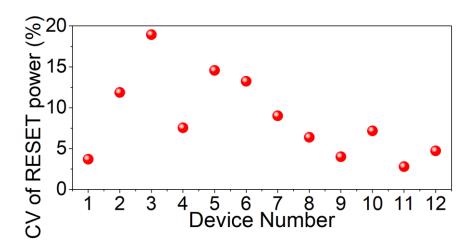

| Figure 24: Coefficient of variation (CV) in the RESET power in MoS <sub>2</sub> devices 44                   |

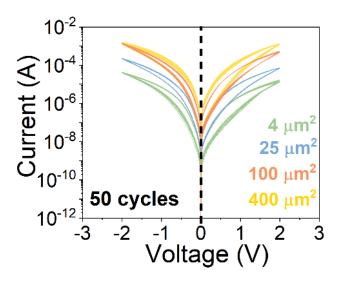

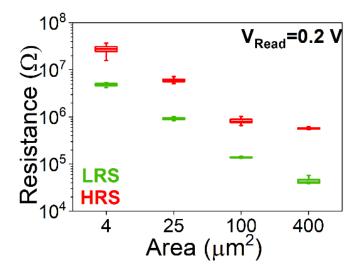

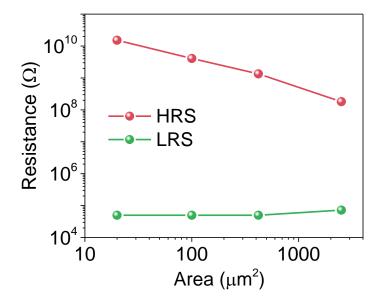

| Figure 25: Area-dependent current scaling in MoS <sub>2</sub> devices of 4 different areas measured for ~50   |

|---------------------------------------------------------------------------------------------------------------|

| cycles in each case                                                                                           |

| Figure 26: HRS and LRS scaling for the 4 different areas, indicating the role played by the interface         |

| at MoS <sub>2</sub> /Ti top electrode. The error bars represent data for 50 cycles                            |

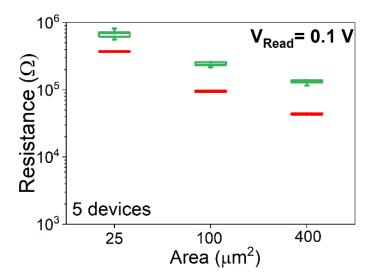

| Figure 27: Area-dependent resistance scaling observed in MoS <sub>2</sub> device indicating the switching     |

| mechanism is non-filamentary. 5 devices of different areas are characterized for one SET-RESET                |

| cycle to extract the OFF and ON state resistance at $V_{\text{Read}}$ = 0.1 V indicating low D-D variability. |

|                                                                                                               |

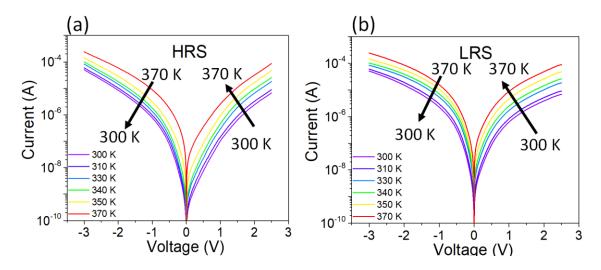

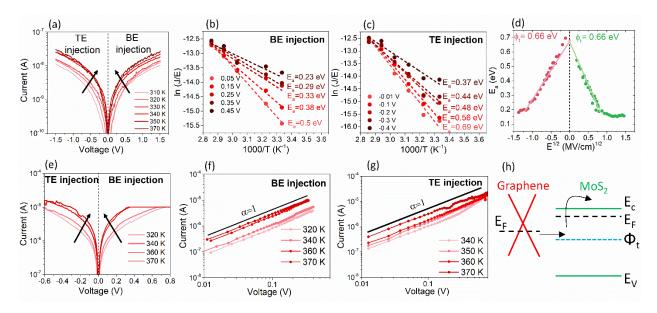

| Figure 28: (a): The I-V characteristics of the MoS <sub>2</sub> device in HRS where the temperature           |

| dependence is observed. (b): The I-V characteristics of $MoS_2$ device in LRS where the temperature           |

| dependence is observed                                                                                        |

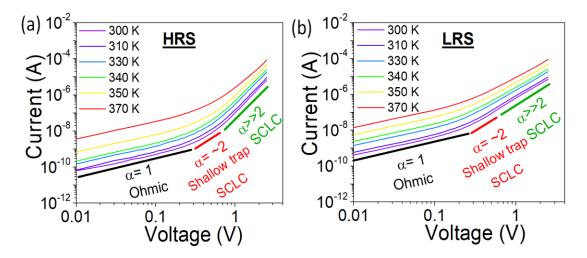

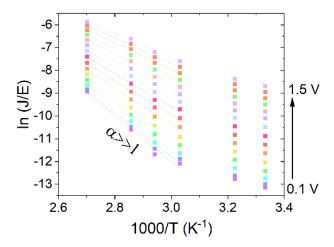

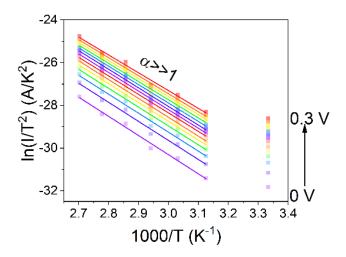

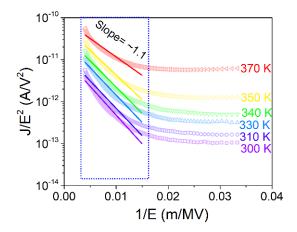

| Figure 29: (a): Temperature-dependent I-V at HRS state showing the increase in OFF current with               |

| increasing temperature. Ohmic conduction in lower voltage regimes of the HRS states. Shallow                  |

| trap SCLC, and SCLC conduction mechanisms at higher voltages in HRS. (b): Temperature-                        |

| dependent I-V at LRS state where the ON current increases with increasing temperature. Ohmic                  |

| conduction in lower voltage regimes of the LRS states and shallow trap SCLC, and SCLC                         |

| conduction mechanisms at higher voltages in LRS                                                               |

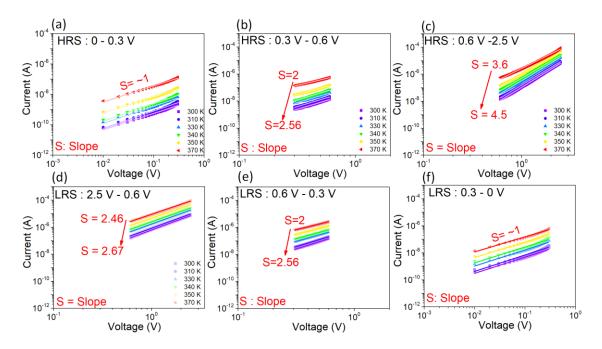

| Figure 30: (a): Double logarithmic plot showing ohmic conduction in HRS at voltages <0.3 V. (b):              |

| Double logarithmic plot showing shallow trap SCLC in HRS where the current follows a near-                    |

| quadratic relation with the applied voltage. (c): Double logarithmic plot showing SCLC in HRS                 |

| where the current follows a higher than quadratic relationship with the applied voltage. (d): Double          |

| logarithmic plot showing SCLC in LRS where the current follows a higher than quadratic                        |

| relationship with the applied voltage. (e): Double logarithmic plot showing shallow trap SCLC in              |

| LRS where the current follows a near-quadratic relation with the applied voltage. (f): Double            |

|----------------------------------------------------------------------------------------------------------|

| logarithmic plot showing ohmic conduction in LRS at voltages <0.3 V                                      |

| Figure 31: I-V fitting using PF model                                                                    |

| Figure 32: I-V fitting using Schottky emission model                                                     |

| Figure 33: I-V fitting using FNT model                                                                   |

| Figure 34: DC potentiation and depression. 52                                                            |

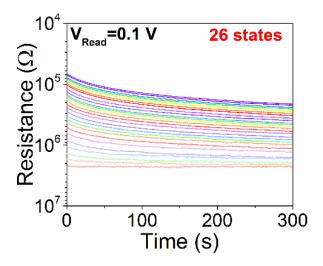

| Figure 35: Retention of ~300 s for 26 distinct states                                                    |

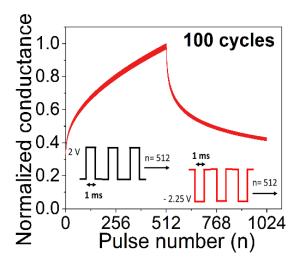

| Figure 36: Weight update characteristics repeated 100 times. Inset: Pulsing scheme for each cycle.       |

|                                                                                                          |

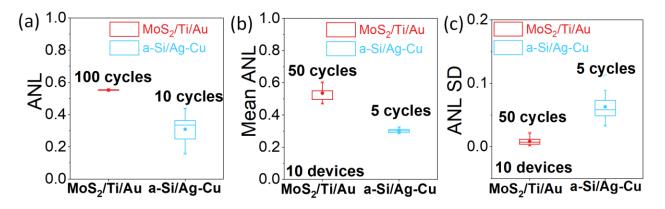

| Figure 37: (a) ANL comparison of $MoS_2$ synapse (over 100 cycles) with a-Si synapse (over 10            |

| cycles). $MoS_2$ synapses exhibit a tighter distribution in the ANL over the entire 100 cycles. (b)      |

| Mean of the ANL extracted for 50 cycles plotted for $10\ MoS_2$ devices shows low variation. This        |

| is compared with the mean of the ANL extracted for 5 cycles plotted for 10 a-Si devices. (c) The         |

| standard deviation (SD) of ANL for 50 cycles in $MoS_2$ devices is compared with the SD of ANL           |

| for 5 cycles in a-Si based devices for 10 devices in each case                                           |

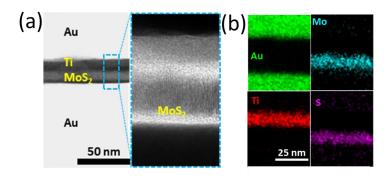

| Figure 38: (a) Cross-sectional TEM of the device. (b) EDS spectra showing the signature of $MoS_2$       |

| and the electrodes; Au (bottom) and Ti/Au (top)                                                          |

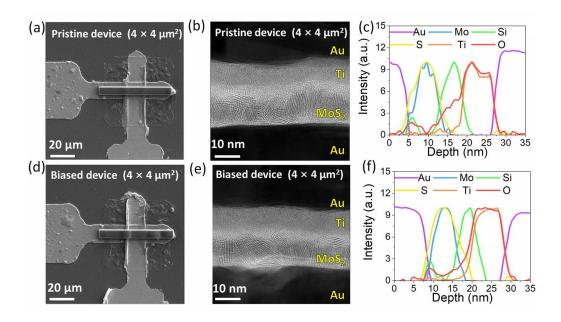

| Figure 39: (a) SEM image of the pristine device with the FIB cutting location marked. (b) Cross-         |

| sectional TEM image of the lateral structure of the same pristine device in (a). (c) EELS map of         |

| the pristine device. (d) SEM image of the biased device (cycled 100 times) with the FIB cutting          |

| location marked. (e) Cross-sectional TEM image of the lateral structure of the same biased device        |

| in (d). (f) EELS map of the biased device. Scale in (a) and (d): 5 $\mu$ m, scale in (b) and (e): 10 nm. |

|                                                                                                          |

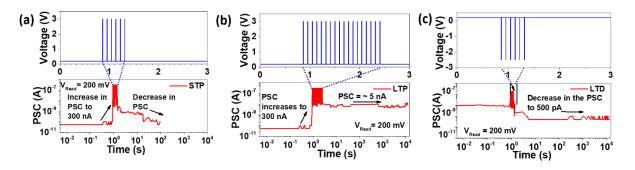

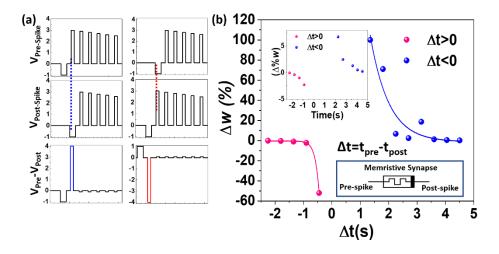

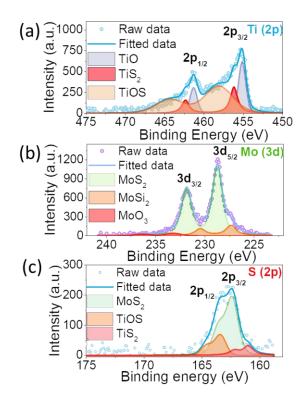

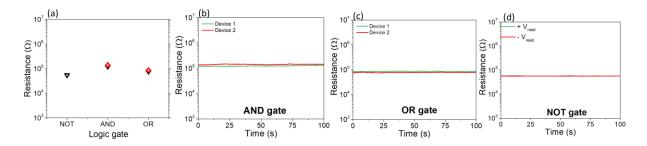

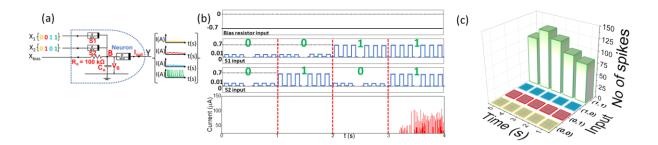

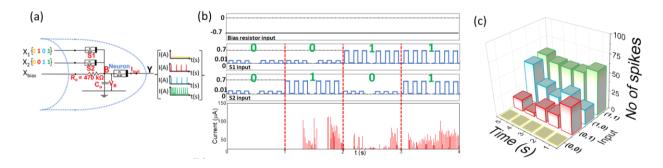

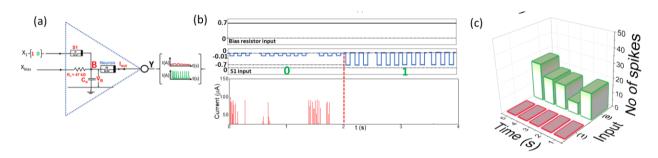

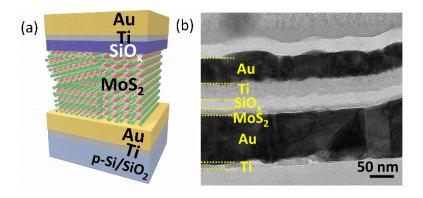

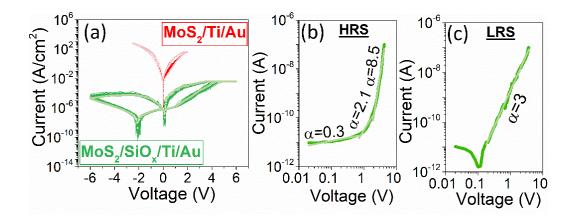

Figure 40: XPS spectra of Ti (2p), Mo (3d) and S(2p). (a) The binding energies of the 2p<sub>3/2</sub> peaks are found at 455.1 eV, 456.2 eV and 457.6 eV correspond to the presence of TiO, TiS<sub>2</sub> and TiOS. (b) Mo  $(3d_{5/2})$  peaks at 228.7 eV, 227.3 eV and 233.1 eV correspond to the presence of MoS<sub>2</sub>, MoSi<sub>2</sub> and MoO<sub>3</sub>. (c) S (2p) spectra indicating the formation of MoS<sub>2</sub>, TiS<sub>2</sub> and TiOS due to the Figure 41: (a): Individual synapse resistance prior to the logic gate implementation. (b): Retention of >100 s observed in MoS<sub>2</sub> synapses prior to the AND gate implementation. (c): Retention of >100 s observed in MoS<sub>2</sub> synapses utilized for OR gate implementation. (d). Retention of >100 s Figure 42: (a): Schematic of two-input AND gate implementation. b: Spiking output with corresponding inputs applied to the circuit. (c): Number of current spikes obtained from MoS<sub>2</sub> Figure 43: (a)Schematic of two-input OR gate implementation. b: Spiking output with corresponding inputs applied to the circuit. (c): Number of current spikes obtained from MoS<sub>2</sub> Figure 44: Schematic of NOT gate implementation. b: Spiking output with corresponding inputs applied to the circuit. (c): Number of current spikes obtained from MoS<sub>2</sub> neuron as a function of Figure 45: (a) Device schematic. (b) Cross-sectional TEM image of the MoS<sub>2</sub> device along the Figure 46: (a) Current through the device measured for MoS<sub>2</sub> device without SiO<sub>x</sub> (Red) and with SiO<sub>x</sub> (Green). Inclusion of SiO<sub>x</sub> decreases the current through the device. (b)SCLC conduction

| mechanism in HRS indicated by the slopes obtained from double log I-V plot. (c) SCLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| conduction mechanism observed in LRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

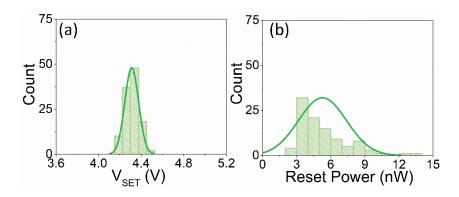

| Figure 47: (a) $V_{SET}$ distribution in $MoS_2/SiO_x/Ti/Au$ device. The device maintains low C-C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| variability in $V_{SET}$ with a range of 0.5 V. (b) Histogram of RESET power distribution. MoS <sub>2</sub> device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| with $SiO_x$ layer exhibits ~ $10^4$ order decrease in the RESET power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

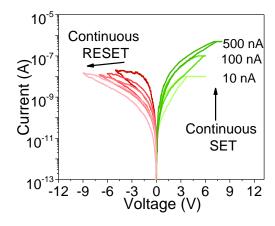

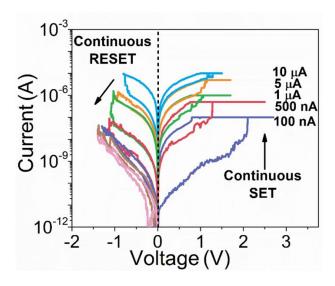

| Figure 48: DC potentiation and depression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

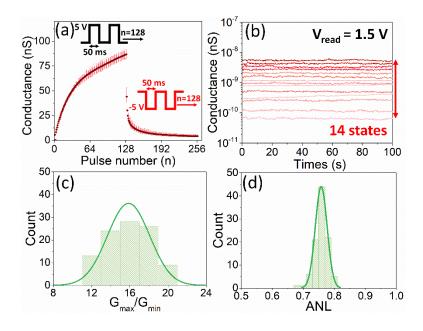

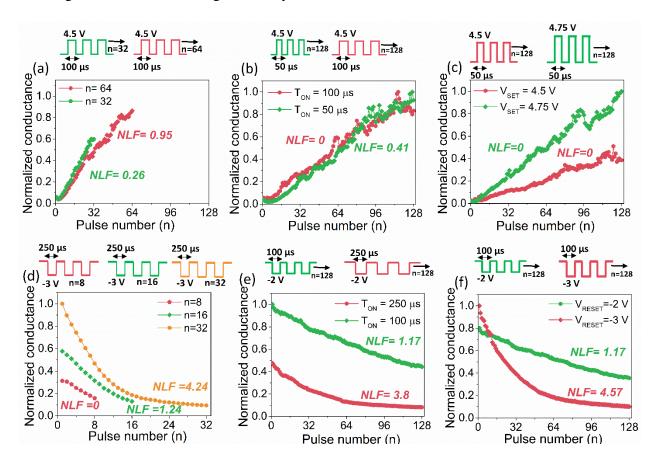

| Figure 49: (a) Weight update variation observed in MoS <sub>2</sub> synapse for 100 cycles showing the mean                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| weight update trajectory. Inset:Pulsing scheme. (b) Retention of >100 s at 14 distinct states. (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The variation of $G_{max}/G_{min}$ for the $MoS_2/SiO_x/Ti/Au$ synapse. The $MoS_2$ with $SiO_x$ layer exhibits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $enhancement\ in\ G_{max}/G_{min.}\ (d)\ ANL\ variation\ observed\ in\ MoS_2/SiO_x/Ti/Au\ synapse\ indicating\ the analysis of the contraction of$ |

| preservation of low C-C variability with the incorporation of SiO <sub>x</sub> layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

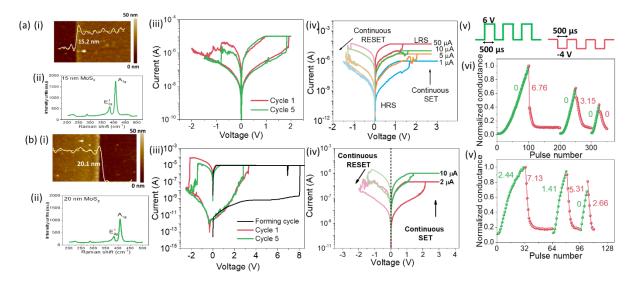

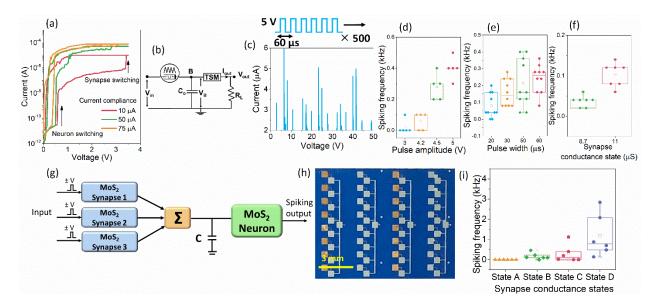

| Figure 50: (a) Device schematic of graphene/MoS <sub>2</sub> /SiO <sub>x</sub> synapse. (b) SEM image of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| graphene/MoS <sub>2</sub> /SiO <sub>x</sub> synapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 51: (a) Raman spectrum of MoS <sub>2</sub> grown directly on graphene. (b) AFM height profile of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| the MoS <sub>2</sub> film. (c) Cross-sectional TEM at the active area indicating the presence of MoS <sub>2</sub> and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SiO <sub>x</sub> . (d) EDS spectra showing the configuration of the device stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

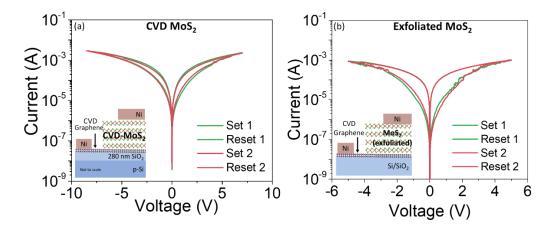

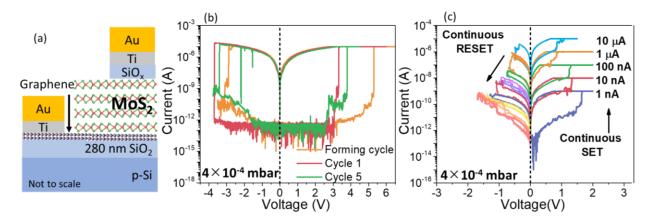

| Figure 52: (a) DC cycling of graphene/MoS <sub>2</sub> /Ni device fabricated using CVD MoS <sub>2</sub> . Inset: Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| schematic. (b) DC cycling of graphene/MoS <sub>2</sub> /Ni device using exfoliated MoS <sub>2</sub> . Inset: Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

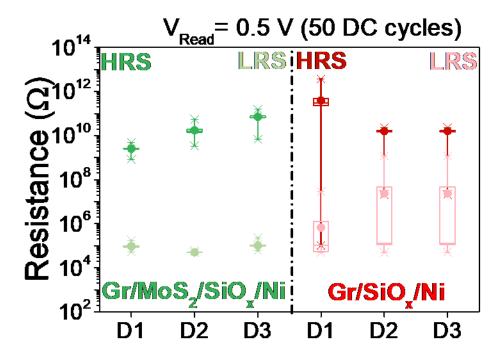

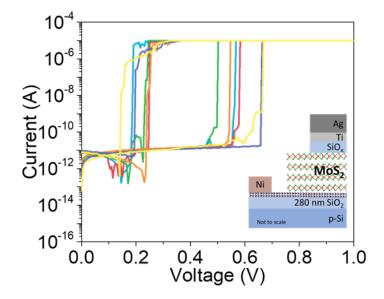

| Figure 53: OFF (HRS) and ON (LRS) state resistance comparison of graphene/MoS <sub>2</sub> /SiO <sub>x</sub> /Ni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| devices with graphene/SiO $_x$ /Ni devices. The devices with MoS $_2$ /SiO $_x$ active medium exhibit low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |