University of Central Florida STARS

**Electronic Theses and Dissertations**

2019

# Automated Synthesis of Memristor Crossbar Networks

Dwaipayan Chakraborty University of Central Florida

Part of the Computer Sciences Commons Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Chakraborty, Dwaipayan, "Automated Synthesis of Memristor Crossbar Networks" (2019). *Electronic Theses and Dissertations*. 6461. https://stars.library.ucf.edu/etd/6461

### AUTOMATED SYNTHESIS OF MEMRISTOR CROSSBAR NETWORKS

by

DWAIPAYAN CHAKRABORTY B.Tech, Maulana Abul Kalam Azad University of Technology, West Bengal, 2015

> A dissertation submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

> > Summer Term 2019

Major Professor: Sumit Kumar Jha

© 2019 Dwaipayan Chakraborty

### ABSTRACT

The advancement of semiconductor device technology over the past decades has enabled the design of increasingly complex electrical and computational machines. Electronic design automation (EDA) has played a significant role in the design and implementation of transistor-based machines. However, as transistors move closer toward their physical limits, the speed-up provided by Moore's law will grind to a halt. Once again, we find ourselves on the verge of a paradigm shift in the computational sciences as newer devices pave the way for novel approaches to computing. One of such devices is the memristor – a resistor with non-volatile memory.

Memristors can be used as junctional switches in crossbar circuits, which comprise of intersecting sets of vertical and horizontal nanowires. The major contribution of this dissertation lies in automating the design of such crossbar circuits – doing a new kind of EDA for a new kind of computational machinery. In general, this dissertation attempts to answer the following questions:

- a. How can we synthesize crossbars for computing large Boolean formulas, up to 128-bit?

- b. How can we synthesize more compact crossbars for small Boolean formulas, up to 8-bit?

- c. For a given loop-free C program doing integer arithmetic, is it possible to synthesize an equivalent crossbar circuit?

We have presented novel solutions to each of the above problems. Our new, proposed solutions resolve a number of significant bottlenecks in existing research, via the usage of innovative logic representation and artificial intelligence techniques. For large Boolean formulas (up to 128-bit), we have utilized Reduced Ordered Binary Decision Diagrams (ROBDDs) to automatically synthesize linearly growing crossbar circuits that compute them. This cutting edge approach towards flow-based computing has yielded state-of-the-art results. It is worth noting that this approach is scalable to n-bit Boolean formulas. We have made significant original contributions by leveraging

artificial intelligence for automatic synthesis of compact crossbar circuits. This inventive method has been expanded to encompass crossbar networks with 1D1M (1-diode-1-memristor) switches, as well. The resultant circuits satisfy the tight constraints of the Feynman Grand Prize challenge and are able to perform 8-bit binary addition. A leading edge development for end-to-end computation with flow-based crossbars has been implemented, which involves methodical translation of loop-free C programs into crossbar circuits via automated synthesis. The original contributions described in this dissertation reflect the substantial progress we have made in the area of electronic design automation for synthesis of memristor crossbar networks.

### ACKNOWLEDGMENTS

First and foremost, I want to thank University of Central Florida and the Department of EECS for giving me the opportunity to pursue a PhD – it has been a transformative experience to say the least. I have endless gratitude towards my advisor, Dr. Sumit Jha, for a large number of things. From him, I have tried to learn how to do "good science", the nuances of doing academic research, the necessary skills to survive in the academic environment and a great many things about life in general. Most of all, I am thankful for his never-ending patience during the times when I might not have been an ideal student. The experiences that he has shared and the conversations we have had, have shaped me as a person at a very fundamental level. After four long years of graduate school, the lessons that I have learned from Dr. Jha are also the ones that I will cherish for the rest of my life.

I am very thankful to Dr. Gary Leavens for providing extremely useful insights on my research and dissertation. I am fortunate to have Dr. Sharma Thankachan, Dr. Rickard Ewetz and Dr. Mengyu Xu on my doctoral dissertation advisory committee – I really appreciate the time and effort that they have invested towards guiding me through this process. I would like to thank all committee members, Dr. Xu, Dr. Ewetz, Dr. Thankachan, Dr. Leavens and Dr. Jha for carefully reading my dissertation and providing useful suggestions.

My doctoral research was supported by the National Science Foundation's projects for Software and Hardware Foundations(award #1438989) and Exploiting Parallelism and Scalability (award #1422257). I would like to acknowledge the support provided through AFOSR Young Investigator Award to Dr. Sumit Jha and the Air Force Office of Scientific Research projects (award number FA9550-16-1-0255). I would like to thank UCF for the financial support provided through Graduate Teaching Assistantship opportunities during Summer 2016, Summer 2017, Fall 2017 and Spring 2018. I would also like to thank Jeanine Clements and Olga Rivera for their help and support.

During the course of my graduate studies, I have had the good fortune of collaborating with Sunny

Raj, Amad Ul Hassen, Julio Gutierrez, Troyle Thomas and Dr. Steven Fernandes. They have some of the brightest minds I have ever encountered, and it has been a joyful experience working with them.

Obtaining a doctorate is undeniably a stressful endeavor, especially when it is put in the context of one's life experiences. As such, it demands that the pursuer is able to wield their mental capabilities to the fullest extent. I want to thank Kristal Pollack and Robert Dwyer for their enormous contribution to this end – they have guided me know myself better and enabled me to effectively deal with my internal turmoil. I would not have survived this phase of my life without the unconditional love of my canine companions, Ringo and Brussels – it has helped me push through the darkest of times and their contribution to my life is unquantifiable. Happiness is real only if it is shared, and I am ever so grateful to have spent time with my friends Vikram, Shane, Maya, Jeanice, Lietsel, Amirfarhad, Freddy, Emily, Alma and Lauren. It's been real.

Lastly, I would like to thank my parents for everything. The sacrifices that they have made over the course of their entire lives have enabled me to reach for my wildest dreams and pursue a doctoral degree in a foreign land filled with uncertainties. I am forever indebted to them for weathering the endless emotional turbulence that I have put them through. This thesis is dedicated to them.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                      | x   |

|----------------------------------------------------------------------|-----|

| LIST OF TABLES                                                       | xii |

| CHAPTER 1: INTRODUCTION                                              | 1   |

| Moore's Law and its limitations                                      | 1   |

| Von Neumann bottleneck and beyond                                    | 3   |

| Memristor - An overview of the fourth fundamental electrical element | 6   |

| CHAPTER 2: LITERATURE REVIEW                                         | 12  |

| Circuit synthesis – A synopsis                                       | 12  |

| Existing memristive and resistive switching devices                  | 14  |

| Crossbar synthesis for computation using sneak paths                 | 16  |

| CHAPTER 3: MOTIVATION                                                | 20  |

| CHAPTER 4: AUTOMATED SYNTHESIS OF LARGE SCALE CROSSBARS WITH RE-     |     |

| DUCED ORDERED BINARY DECISION DIAGRAMS                               | 21  |

| Crossbars as abstractions                                            | 21  |

| Binary Decision Diagrams (BDDs) and Reduced Ordered Binary Decision Diagrams |    |

|------------------------------------------------------------------------------|----|

| (ROBDDs)                                                                     | 22 |

| Inductive mapping of ROBDDs to crossbar circuits                             | 23 |

| CHAPTER 5: CROSSBAR SYNTHESIS USING MODEL COUNTING                           | 39 |

| Synthesis of crossbars with bidirectional memristive switches                | 39 |

| Synthesis of crossbars with unidirectional memristive switches               | 43 |

| CHAPTER 6: USING FLOW-BASED CROSSBARS FOR IN-MEMORY EXECUTION                |    |

| OF COMPUTE KERNELS                                                           | 47 |

| Compute Kernel                                                               | 48 |

| From C Kernel to Intermediate Representation                                 | 49 |

| Intermediate Representation to Boolean Decision Diagram                      | 49 |

| Illustrative Example                                                         | 51 |

| CHAPTER 7: EXPERIMENTAL RESULTS                                              | 53 |

| ROBDD based synthesis                                                        | 53 |

| Model counting based synthesis                                               | 56 |

| In-memory execution of compute kernels                                       | 58 |

| CHAPTER 8: CONCLUSION                                                        | 60 |

| CHAPTER 9:   | FUTURE  | WORK . | <br>• • | <br> |      | <br> |  |  | • | <br>• | <br> | 62 |

|--------------|---------|--------|---------|------|------|------|--|--|---|-------|------|----|

|              |         |        |         |      |      |      |  |  |   |       |      |    |

| LIST OF REFI | ERENCES |        |         |      | <br> | <br> |  |  |   |       | <br> | 63 |

## LIST OF FIGURES

| 1.1 | The Von Neumann architecture of a programmable computer                           | 3  |

|-----|-----------------------------------------------------------------------------------|----|

| 1.2 | Memory hierarchy with on-chip cache memory                                        | 4  |

| 1.3 | State transition behavior of a memristor                                          | 8  |

| 1.4 | Memristor in ON and OFF states                                                    | 9  |

| 2.1 | Crossbar implementing $\neg A \land \neg B \land \neg C$ with two input instances | 17 |

| 2.2 | Crossbar implementing 4-bit parity checking with two input instances              | 18 |

| 2.3 | Crossbar implementing a full adder with two input instances                       | 19 |

| 4.1 | Nodes at a single level of a ROBDD and their children                             | 24 |

| 4.2 | Mapping a subgraph to a crossbar, as a basis for the inductive hypothesis         | 25 |

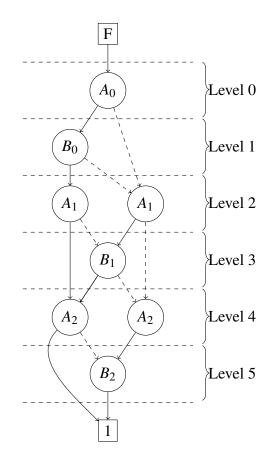

| 4.3 | Inductive synthesis of memristor crossbar circuits based on ROBDDs                | 27 |

| 4.4 | ROBDD representing the most significant bit of 3-bit binary addition              | 29 |

| 4.5 | Level-by-level mapping of ROBDD to a crossbar                                     | 30 |

| 5.1 | Compact crossbar circuit for computing MSB of 2-bit binary addition               | 39 |

| 5.2 | Compact crossbars synthesized using model counting                                | 42 |

| 5.3 | Switching states of 1D1M devices                                                  | 43 |

| 5.4 | A crossbar circuit computing the Sum, $C_{out}$ and $\neg C_{out}$ of 1-bit binary addition | 45 |

|-----|---------------------------------------------------------------------------------------------|----|

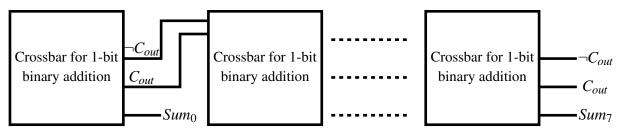

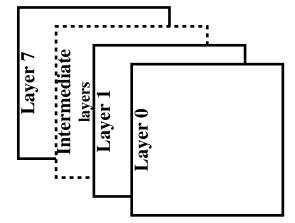

| 5.5 | 3D stacking of crossbar circuits and external connections between them                      | 46 |

| 6.1 | ROBDD for the MSB of 4-bit binary subtraction                                               | 50 |

# LIST OF TABLES

| 2.1  | Overview of switching devices                                                       | 15 |

|------|-------------------------------------------------------------------------------------|----|

| 7.1  | Size comparison of crossbars for <i>n</i> -bit Boolean addition                     | 53 |

| 7.2  | Delay (in picoseconds) to compute the MSB of <i>n</i> -bit binary addition          | 54 |

| 7.3  | Power consumption (in $\mu W$ ) to compute the MSB of <i>n</i> -bit binary addition | 54 |

| 7.4  | Delay (in picoseconds) for selected benchmarks                                      | 55 |

| 7.5  | Power consumption (in $\mu W$ ) for selected benchmarks                             | 55 |

| 7.6  | Simulation results for <i>n</i> -bit Boolean addition                               | 56 |

| 7.7  | Comparison of crossbars sizes for <i>n</i> -bit binary addition                     | 56 |

| 7.8  | Delay (in picoseconds) for <i>n</i> -bit binary addition                            | 57 |

| 7.9  | Power consumption (in $\mu W$ ) for <i>n</i> -bit binary addition                   | 57 |

| 7.10 | Simulation results for crossbars implementing a simple edge detection kernel        | 58 |

| 7.11 | Simulation results for crossbars implementing RGB edge detection                    | 59 |

### **CHAPTER 1: INTRODUCTION**

Moore's Law and its limitations

Over the last five decades, Moore's Law [1, 2], has been a driving factor for immense technological and societal progress. While the advancements have indeed validated the status of Moore's observations and projections as a "law" they certainly did not start out as such. The seminal paper simply explores the trend of fabrication parameters – namely approximate component count, die area and device density - and breaks down the complexity of chip fabrication into its contributing factors. These factors are a function of the ones that had previously been observed - die size, dimension reduction, the product of the above two and a generous smattering of device and circuit design cleverness. Moore then proceeds to project the complexity curve for the future, which has shown to be the most impactful contribution of the paper so far, since it predicts the increase in component count per chip with time. Akin to how Moore's Law paints a picture for the future of chip design, Dennard scaling [3] examines possibilities for the scaling of devices - in this case, MOSFETs. The two-dimensional effects of the semiconductor material are kept at a sub-perceptual level, and the authors proceed to develop a design methodology to manufacture devices that have a marked performance improvement over contemporary devices. Further, physical limitations for MOSFET fabrication are investigated and the authors identify a set of problems that need to be solved in order to achieve better performance. We can thus see how a potent combination of chip design methodology and device fabrication technology had driven the industry to its current heights. With the passage of time and advent of technology, Moore's Law was shown to be less of a prediction and more of an oracle guiding the innovation of computational machines [4]. It has held true throughout the MSI (medium scale integration), LSI (large scale integration) and VLSI (very large scale integration) stages of circuit fabrication.

As had been projected by Moore's Law, transistor scaling has kept on improving. However, Dennard scaling hit a roadblock as CMOS transistors started replacing MOSFETs - this has been marked by a shift from micrometer ( $\mu$ m) scale to nanometer (nm) scale devices. There have been persistent efforts towards technological advancements, while utilizing Moore's Law as much as possible. For example, interesting breakthroughs have been made in the area by using self-aligned double gate MOSFET structures (FinFET) [5], which are projected to scale down to as small as 10nm. Improvements have been made to better the chip density as well, notably by three dimensional layering of active devices [6]. Researchers have also proposed a solution to enhance the energy efficiency of CMOS-based architectures [7] by intuitively utilizing voltage scaling techniques. Despite these leaps in technology and many similar ones, scaling down devices has kept on getting more and more difficult, each transition in scale bringing with it a new set of challenges and problems to be solved [8]. As the device dimensions are reduced, the traditional challenges posed by capacitance and resistance become more daunting, dielectric properties of materials interfere more, and physical properties like orientation of silicon lattice structures, wafer thickness and mechanical strain start having more effects on the device behavior. For instance, a cumulative effect of the above hurdles and the thermal Johnson-Nyquist noise [9] has been identified, which threatens to completely disrupt the correct behavior transistors at some point in the future. The greatest hindrance against the continuous downscaling of transistors is faced when the quantum mechanical properties (intrinsic to the semiconductor material) come into play. Such quantum effects are explored in [10], and to a greater extent in [11]. A compelling argument against the continuation of Moore's law can be drawn from the Heisenberg uncertainty, which establishes an upper bound on the constant miniaturization of semiconductor devices. Essentially, a transistor will stop behaving in a deterministic manner at a small enough scale, due to the quantum mechanical properties of matter. Given the above set of limitations (and many similar ones), it is reasonable to conjecture that Moore's Law is approaching its eventual demise. In a such a scenario it is only prudent to turn our attention to computational techniques which are not reliant on Moore's Law, thus ensuring undeterred and uninterrupted technological progress.

#### Von Neumann bottleneck and beyond

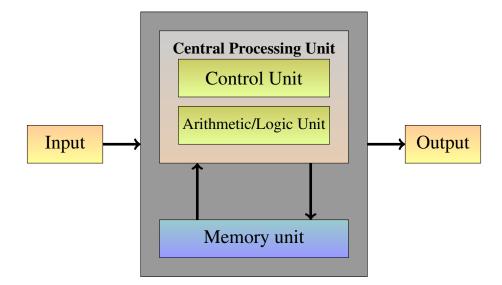

The Von Neumann architecture [12] was the first architecture that introduced the concept of storedprogram computers - a development that sent ripples through the landscape of computational science over the following decades following its establishment. The architecture can be explained very simply by breaking it down into its modular components. The Von Neumann computer in Figure 1.1 can be interfaced with input and output devices, but its core computational unit is what interests us. It features a memory unit containing programs and data, which are fetched and processed by the central processing unit (CPU). The CPU itself consists of the arithmetic/logic unit (ALU) along with registers and a control unit consisting of an instruction register and program counter. The mathematical and engineering foundations for this architecture were subsequently laid in [13]. Von Neumann himself was acutely aware of some of the limitations of the architecture [14], and had pondered the possibility of using multiple computers in parallel in order to perform arduous computations. However, the major flaw in the Von Neumann architecture was the processor-memory bottleneck, as identified in [15]. As we know, there exists a sizable gap between processor and memory performance [16].

Figure 1.1: The Von Neumann architecture of a programmable computer

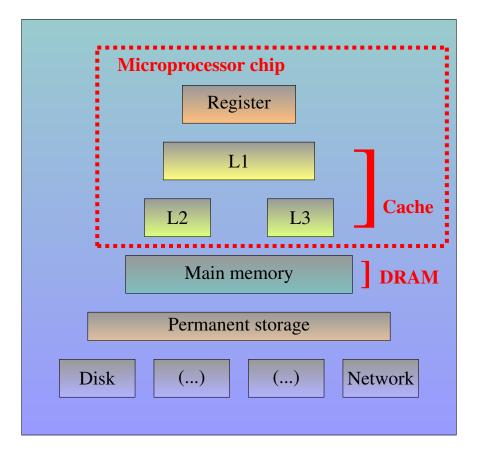

Figure 1.2: Memory hierarchy with on-chip cache memory

Additionally, the bus connecting the processor and the memory will always have a limited bandwidth, thereby throttling performance even further. Given this scenario, the Von Neumann architecture has ceased to be of much convenience in the current times. Despite the dynamic random access memory (DRAM) performance improving exponentially, it has been shown [17] that the processor-memory gap will also increase in an exponential manner, ultimately hitting a memory wall. One of the major approaches to tackle the bottleneck was the progress of on-chip cache memory as a component of the existing memory hierarchy [18], as shown in Figure 1.2. Cache memories boost performance mainly by pre-fetching instructions and data from the main memory (RAM) onto the microprocessor, thereby eliminating the need to use the limited-bandwidth bus in certain cases. However, issues like invalidation misses give rise to bad cache behavior [19] when trying to handle larger problems. With the development of faster microprocessors, there will be greater demands placed on memory bandwidth, more specifically pin bandwidth [20], further choking the performance of future computers. While the Von Neumann architecture had once provided a simple and highly effective blueprint for computer design by abstracting away a great deal of engineering problems, it can no longer be utilized due to the plethora of disadvantages that have been exposed over time.

The eradication of the Von Neumann bottleneck has been targeted by a number of different approaches. A technique to negate the processor-memory bottleneck is to use the data-flow based programming paradigm. This model reduces the need to constantly fetch data by implementing data-driven instructions, i.e. a given instruction is only executed if and if its required operands are fetched at the end of a preceding instruction. Hence, data that would otherwise be fetched and overwritten (without being used) is no longer fetched, thereby reducing the effects of the bottleneck. The authors of [21] propose a processor design that employs the data-flow based model and is capable of performing highly parallel computations with low latency. One of the major pathways of research is provided by computation-in-memory (CIM) approaches. In [22], the authors propose a complete CIM-based parallel adder architecture which is shown be smaller, faster and more energy efficient than the state-of-the-art. A CIM architecture essentially gets rid of separate processor and memory units by using a crossbar. A crossbar is a circuit consisting of overlapping vertical and horizontal nanowires, with switchable memory elements placed at every junction where the wires intersect. Hence, memory can be stored at this location and computational operations are triggered and achieved by the communication network and external control circuitry. The communication network can be generalized as a two-dimensional mesh-based interconnection network as exhibited in [23], where the authors utilize this abstraction to implement a the highly capable Tile64 processor architecture powered by on-chip interconnects. It is worth noting that a crossbar architecture is maintained as the computational core of the system. Perhaps one of the most lucrative possibilities offered by CIM architectures is their capability to seamlessly accelerate parallel executions and algorithms. A crossbar-based template for such applications is introduced in [24] consisting of scheduling, placement and routing information - aptly named a "skeleton". This solution maps the

data flow of some common parallel algorithms to crossbars and assesses the performance, space complexity and energy efficiency of the solution. A feasible alternative to having an end-to-end CIM architecture, a processor-in-memory (PIM) architecture can be used in synergy with a conventional Von Neumann computer to accelerate the execution of a given set of instructions [25]. An in-depth exploration of true potential of the PIM architecture is performed through the development of the Gilgamesh framework [26]. The framework accomplishes petaflops scale computing by implementing features like advanced task and data virtualization, adaptive resource management and object-based runtime management of system elements. At this point, we can observe that taking care of the Von Neumann bottleneck essentially entails the embedding of non-memory operations in the memory itself. In a similar vein of thought, logical operations are also performed in-memory [27] - a novel framework called logic-in-memory (LiM), which utilizes interpolation memory and a seed table with simple arithmetic logic is synthesized and shown be significantly better than conventional computing methodologies for a specific set of applications. One of the ways of achieving massively parallel computation had been through associative processors [28], which basically combines enormous arrays of traditional SIMD processors and memory (based on Von Neumann architecture). With the eventual demise of Moore's Law on the horizon, it would only be judicious to adapt such a simple, yet versatile, architecture to next generation technology like resistive memory devices [29]. A diligent survey of the above-mentioned literature reveals that crossbar-based architectures hold a great deal of promise towards yielding considerable breakthroughs in this field. At the heart of most crossbar circuits lie memristors or memristor-like devices [30], which we will discuss in greater details in subsequent sections.

#### Memristor - An overview of the fourth fundamental electrical element

In 1971, Leon Chua hypothesized that in addition to resistor, capacitor and inductance, there existed a fourth fundamental electrical element. This new element, which demonstrated a relation between flux linkage and electrical charge, was termed as a "memristor" [31] - an amalgamation of memory and resistor. This name arose from the fact that a memristor's resistance varies with the net current flow through it and the resistance state would be maintained even if the device was disconnected from a power source, thereby giving it the property of non-volatile memory. It was further observed that memristors can be charge-controlled or flux-controlled. Given that we have *voltage v, current i, charge q* and *flux linkage \phi* we can define the following:

$$d\phi(q) =$$

rate of charge of charge with respect to the flux linkage (1.1)

$$dq(\phi) =$$

rate of change of flux linkage with respect to the charge (1.2)

Based on the above definitions, following expressions can be defined:

$$M(q) = \frac{d\phi(q)}{dq} \tag{1.3}$$

$$W(\phi) = \frac{dq(\phi)}{d\phi} \tag{1.4}$$

Where M(q) is termed as the memristance (since it has dimensional equivalence with resistance) and  $W(\phi)$  is termed as the memductance (since it has dimensional equivalence with conductance). Hence, the voltage across a charge-controlled memristor (at time *t*) and the current of a fluxcontrolled memristor (at time *t*) is characterized respectively as:

$$v(t) = M(q(t))i(t)$$

(1.5)

$$i(t) = W(\phi(t))v(t) \tag{1.6}$$

Hence we can see that the state of a given memristor can be changed by either changing its charge or its flux linkage, but not both. As we will see later, this has produced voltage-controlled and current-controlled memristive devices. Essentially, the internal resistance of the memristor is manipulated to change it's state. A memristor has two different terminals which correspond to positive (p) and negative (n) polarities.

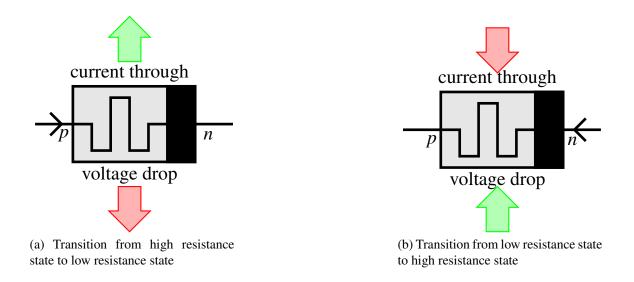

Figure 1.3: State transition behavior of a memristor

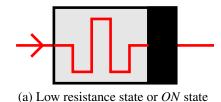

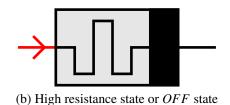

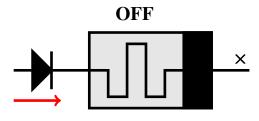

The behavior of a memristor device can also be explained in a simpler manner. From Figure 1.3 we can see that the voltage drop across the memristor decreases and the current across it increases as it transitions from a high resistance state (HRS) to a low resistance state (LRS), when an external stimulus (current or voltage) is applied at the p terminal. In contrast, the voltage drop across the memristor increases and the current across it decreases when the as it transitions from a low resistance state (LRS) to a high resistance state (HRS), when an external stimulus (current or voltage) is applied at the *n* terminal. The HRS can be related to the highest possible resistance that the device can have and the LRS to the lowest possible state the device can have. Ideally, the HRS will be infinity (infinitely high resistance) and the LRS will be zero (no resistance at all). Therefore, we can say that the HRS is the OFF state and the LRS is the ON state. Hence, it can be said without doubt that the memristor device can be used as switch, and the transition from LRS to HRS (and vice versa) is thereby termed as "switching" behavior. A memristor in the LRS allows current flow across it, akin to a closed circuit or a turned-on switch. A memristor in the HRS allows no current across it, similar to an open circuit or a turned-off switch. This behavior is shown in Figure 1.4, and is limited by physical constraints, i.e. ideal behavior is not practically achievable.

Figure 1.4: Memristor in ON and OFF states

Memristors were further investigated and characterized using Lissajous figures by Chua [32]. A memristor's transitional behavior is identified as a pinched hysteresis loop, which underlies the special properties associated with a memristor. This makes it possible to explore the possibilities of using a memristor as an interesting non-linear element for computation, even though we will stick with its behavior as a switch for the scope of this document. Nearly 37 years after the conception of the memristor, a  $TiO_{2-x}$ -based discrete memristor device was fabricated [30] in 2008. However, it must be taken into account that this device did not use electromagnetism to change the internal state, even the "ideal" memristor requires a change in the electromagnetic field to change its internal state. It was recently argued [33] based on this fact that the missing memristor has not been found and is likely a physical impossibility – this is a debate that is currently active in the scientific community. The distinction between a device being an "ideal" memristor and it behaving like one is a small but important one. Nevertheless, such devices have tremendous potential to change the landscape of computer architecture and computer science in general. Let us now take a look at some interesting applications of memristive devices, which are commonly known was resistive RAM (RRAM or ReRAM) devices.

The authors of [34] have done a very thorough job of providing a balanced overview of the field of non-volatile memory devices, where both their applications solely as memory devices as well as their future as computational elements are examined. A number of different technologies are surveyed, and memristive devices are shown to be the only branch where full physical implementation has been achieved. Due their non-volatile property, ReRAMs are primarily being employed as memory elements in novel memory architectures. The authors of [35] have proposed a compelling design for 3D stacked ReRAM caches – a design which has been shown to be at least as good as existing DRAM technology in most cases. However, use of memristors as a component for in-memory computation is arguably a more exciting area of research. A framework for performing stateful logic using memristor-based nanoscale crossbar circuits has been provided in [36]. While purely memristive circuits are shown to be rather intractable in case of large problems, it is possible to scale up the solution when each memristor is paired with a bi-directional diode. Even though a memristor can be used as a binary switch, its pinched hysteresis indicates that it also has analog properties that can be exploited. In [37] simple addition has been performed by combining this very property with cyclical programming. Here the output is not binary, but a conductance level at a fixed voltage. The crossbar fabric inherently supports parallel computation, since the state of all the memristive switches in a crossbar circuit can be changed in parallel quite trivially. This feature is utilized in [38], where the authors probe the application of memristive crossbar networks to the field of massively-parallel computing. A maze can be considered an abstraction for a wide variety of computational problems, and the authors have devised an algorithm to solve mazes, thereby extending the applicability of their approach a a number of different fields. At the same time, foundational research has been continuously been going on, as in [39]. It has been demonstrated that Boolean logic operations can be reliably implemented using a single memristor - the trick lies in applying the input bits periodically, in a sequential manner instead of applying them all at once. While this approach compromises the possibility of parallelism, the minimal size and high power efficiency more than make up for it. One of the impressive displays of using memristors at the core of parallel computation can be found in [40]. Not only has a design been proposed for performing parallel matrix multiplication, the scheme has also been shown to achieve a performance that is orders of magnitude better than existing methods. Finally in [41], a tentative yet promising solution has been suggested in order to unleash the potential of in-memory computation with memristors for big-data applications. This is a significant result as it shows that memristors are not a short-lived trend, but are capable of solving some of the largest and most complex computational problems that we are faced with today. Of course, there are many more

examples that validate the true potential of memristors to solve real-world problems – the above examples capture a reasonable picture of the more relevant sections of that spectrum.

### **CHAPTER 2: LITERATURE REVIEW**

Circuit synthesis – A synopsis

As is known, synthesis is one of the major steps in circuit design. This can refer to the synthesis of network parameters or synthesis of the network topology. The synthesis of network parameters continues to be a critical aspect for analog circuit design. Early work in synthesis of network topology has been done in [42], where the authors had developed a symbolic circuit design tool SYN. The circuit constraints were provided to the tool, which has been shown to provide clear and concise results through incremental deduction. Perhaps one of the first overlaps between the field of algorithms and circuit synthesis can be found in [43]. In this case, the authors had utilized the branch-and-bound technique for constrained optimization of a two-stage CMOS-based operational amplifier design. With the passage of time and the advent of technology, the demand for more complex circuits were needed, thereby demanding more powerful automated synthesis tools. A knowledge-based approach towards such tools is presented in [43]. The OASYS tool equips the user with a hierarchical design methodology and a systematic exploration of the design space in order to produce circuits even for high performance systems. The fidelity of the circuits are as important as their complexity, which is why there is a necessity for tools that ensure reliable circuit synthesis even if a mismatch exists [44]. The set of constraints necessary for circuit synthesis can often be navigated by using innovative representations and search techniques [45] or by integrating existing techniques into new design methodologies [46]. Accurate synthesis for analog circuits can often be achieved by accounting for inherent stochastic effects (like parasitic capacitance) in a more energy-efficient manner [47] or by introducing error correction within the circuits themselves [48]. Synthesis techniques are equally useful in cases of re-configurable circuits [49], which enables rapid prototyping to aid in the advent of re-configurable device design. Circuit synthesis is not limited to analog or digital applications and has been used for synthesis of reversible [50, 51] and quantum [52, 50] circuits. This progress has facilitated the usage of quantum computing principles to synthesize Boolean circuits [53]. Tools have also been developed to synthesize approximate circuits [54], as well as for the efficient synthesis of robust circuits [55]. Circuit synthesis at higher levels of abstraction [56] with a mathematically rigorous basis has also been explored. In contrast, stochastic search methods have also been effectively utilized [57] to synthesize novel architectures for a sub-class of circuits. Furthermore, automated design also been applied to obtain dynamic configurations for FPGA's [58]. The power of automated synthesis can also be extended to come up with circuits that not only have lower space requirements, but also capable to delivering optimal or near-optimal power consumption [59].

One of the earlier developments if the field of logic synthesis was demonstrated through the now well-known Karnaugh maps [60]. A symbolic method for synthesizing combinational circuits [61] was demonstrated which yielded functional, but not necessarily optimal circuits. This was soon followed by the work by McCluskey [62], which laid the groundwork for subsequent synthesis of combinational circuits executing Boolean logic. Multiplexers were identified [63] as modular components that could be used for automatically synthesizing combinational circuits - a development that would later be utilized widely in the field of circuit design as well as automated circuit synthesis. The advent of both computer hardware and software yielded one of the earliest circuit synthesis tools [64]. While MACDAS was capable of producing functional combinational circuits, there was still a necessity for tools what could construct sequential circuits. This gap was filled by SIS [65, 66], which truly became one of the landmark tools in automated circuit synthesis. Its utility was aggregated by the fact that SIS incorporated a number of optimization techniques within the synthesis process - this resulted in combinational circuit designs which were not only functional but also optimal or near-optimal. Once such potent tools were developed, the next significant undertaking largely involved the improvement of the said tool. Decompositional logic synthesis [67] and multi-level logic synthesis [68] were some of the numerous approaches that were probed in an attempt to further the contemporary automated synthesis techniques. The power of Boolean satisfiability solving (SAT solving) was applied [69] for producing asynchronous circuits, which was soon followed by the development of the Tangram framework [70]. The framework was then

extended as the BALSA system [71] – a tool which would later be used during the development of self-timed ARM processor cores. The problem of synthesizing sequential synchronous logic circuits has been attacked in a similar fashion [72], with the added objectives to optimize cycle time. The research in this direction yielded circuits with lower delay and synthesis algorithms which were compatible with the existing technologies at the time. The growing interest for research in the field saw produced some interesting applications like the synthesis of circuits with concurrent error detection with a reduced area requirement [73], as well as development of larger, more complex pass transistor-based circuits using Boolean decision diagrams (BDDs) [74]. Similar ideas had been explored at an earlier time, with goals to minimize power consumption [75]. Among many other publications, the significance of representation and manipulation of combinational circuits as abstract data structures was consolidated in [76].

#### Existing memristive and resistive switching devices

The physical switching devices form the basis for realization of the synthesized logic and architecture. A brief summary of notable memristive and resistive switching devices has been provided in Table 2.1. There also exist a number of comprehensive reviews of such devices in current literature. The authors of [77] explore the resistive switching phenomena in transition metal oxides. While [78] takes an in-depth look at a sub-class of the devices developed through oxidation-reduction (redox) methods and their inherent nanoionic mechanisms, [79] utilizes the NEXAFS tool to gain a more profound insights into the behavior of  $TiO_2$ -based devices specifically. The fabrication challenges often arise from an intent to create smaller devices – reducing the space requirement for the the switching mechanisms and actual materials both play a crucial role.

A broad perspective of existing technologies and devices is given by [109, 110]. The nature of the sub-class of thin film resistive switching devices has been thoroughly studied in [111], and the role of contemporary devices for primarily neuromorphic computing has been considered in [112].

| Year | Device | Materials                                       | Structure                                          | Width                    |  |  |  |  |

|------|--------|-------------------------------------------------|----------------------------------------------------|--------------------------|--|--|--|--|

| 2006 | [80]   | TiO <sub>2</sub> /TiN                           | Thin film                                          | 50nm                     |  |  |  |  |

|      | [81]   | Cu/SiO <sub>2</sub>                             | u/SiO <sub>2</sub> Programmable metallization cell |                          |  |  |  |  |

| 2007 | [82]   | Ti/ZrO <sub>2</sub> /Pt                         | Metal-insulator-metal                              | 250µm                    |  |  |  |  |

|      | [83]   | Cr/SrTiO <sub>3</sub>                           | Metal-insulator-metal                              | 500nm                    |  |  |  |  |

|      | [84]   | $ZrO_2/Zr+$                                     | Sandwich                                           | 50-800µm                 |  |  |  |  |

|      | [85]   | Si/a-Si×Ag                                      | Core/shell nanowires                               | 20nm                     |  |  |  |  |

| 2008 | [86]   | Cu/ZrO <sub>2</sub> :Cu/Pt                      | Sandwich                                           | 3-20µm                   |  |  |  |  |

|      | [30]   | $TiO_2/TiO_{2-x}$                               | Thin film                                          | 3nm                      |  |  |  |  |

|      | [87]   | NiO/n-doped Si                                  | Metal-insulator-semiconductor                      | 160nm                    |  |  |  |  |

|      | [88]   | Si/SiO <sub>2</sub> /Ti/Pt/TiO <sub>2</sub> /Pt | Thin film                                          | $50$ nm- $5\mu$ m        |  |  |  |  |

| 2009 | [89]   | Ti/Pt/TiO <sub>2</sub> /Pt                      | Electroformed substrate                            | 70nm                     |  |  |  |  |

|      | [90]   | Au/ZnO/stainless steel                          | Thin film                                          | 35nm                     |  |  |  |  |

|      | [91]   | Pt/TaO <sub>x</sub> /Ta                         | Stack                                              | $100\mu m^2$ (area)      |  |  |  |  |

|      | [92]   | Ag/a–Si/p–Si                                    | Filament                                           | 50nm                     |  |  |  |  |

| 2010 | [93]   | Al/GO/ITO                                       | Metal—insulatormetal                               | 30nm                     |  |  |  |  |

|      | [94]   | Fe-doped SrTiO <sub>3</sub>                     | Thin film                                          | 35nm                     |  |  |  |  |

|      | [95]   | Pt/TiO <sub>2</sub> /Pt                         | Metal—insulatormetal                               | 140nm                    |  |  |  |  |

|      | [96]   | ZnO                                             | Thin film                                          | 82µm                     |  |  |  |  |

| 2011 | [97]   | TiN/Al <sub>2</sub> O <sub>3</sub> /Pt          | Metal—insulatormetal                               | 50nm                     |  |  |  |  |

|      | [98]   | p-Si/HfO2/p-Si                                  | Filament                                           | 50nm (HfO <sub>2</sub> ) |  |  |  |  |

|      | [99]   | Ag/a-Si/Pt                                      | Filament                                           | 100nm                    |  |  |  |  |

| 2012 | [100]  | $Pd/Ta_2O_{5-x}/TaO_y/Pd$                       | Thin film                                          | 0.5-2µm                  |  |  |  |  |

|      | [101]  | SiO <sub>x</sub>                                | Thin film                                          | 15-120nm                 |  |  |  |  |

| 2013 | [102]  | SiO <sub>2</sub> /Si                            | Cross-point                                        | 8nm                      |  |  |  |  |

| 2015 | [103]  | Ti/ZnO/Mo                                       | Metal—insulatormetal                               | 50-500nm                 |  |  |  |  |

| 2017 | [104]  | Pt/Ta <sub>2</sub> O <sub>5+x</sub> /Ta         | Metal—insulatormetal                               | 20nm                     |  |  |  |  |

|      | [105]  | Pt/HfO <sub>2</sub> /TiN                        | Filament                                           | 300nm                    |  |  |  |  |

| 2018 | [106]  | Cu/MoS <sub>2</sub> /W <sub>2</sub> N           | Thin film                                          | 200 nm                   |  |  |  |  |

|      | [107]  | HSQ                                             | Metal—insulatormetal                               | $200\mu$ m- $800\mu$ m   |  |  |  |  |

| 2019 | [108]  | Ag/HfAlOx/Pt                                    | Metal—insulatormetal                               | 136nm                    |  |  |  |  |

### Table 2.1: Overview of switching devices

Memristors are are capable of showing controllable, yet probabilistic, switching behavior in [113] – an interesting phenomenon of critical importance for practical stochastic computing frameworks.

Redox devices are revisited in [114], where their applicability with respect to Boolean function realization is inspected. Finally, a rigorous survey of current resistive switches manufactured using metal oxides is presented in [115]. All in all, this section provides a broad, surface-level picture of some compelling memristive and resistive switching devices.

#### Crossbar synthesis for computation using sneak paths

In any given graph, a path is said to exist between two nodes if there exists a set of edges that connects the two nodes. In other words, existence of a path implies that one node is reachable from the other. In a crossbar, a connection might or might not exist between two nanowires. If a connection *does* exist, then a current flow introduced in one of the nanowires at time t will be observable at the other nanowire at a time  $(t + \varepsilon)$ , where  $\varepsilon$  is the short amount of time it takes for the current to flow from one point to another. When an undesired path exists, the problem is termed as a "sneak" path. However, the authors of [116, 117] have managed to turn this potential drawback into a computational mechanism. A Boolean formula is mapped into a crossbar with the following properties:

- There must exist memristors in the crossbars corresponding to literals in the Boolean formula.

- The memristors must be switched ON or OFF, depending on the input instances.

- A current flow must be introduced in one of the nanowires, and the index of the nanowire is constant for a given formula.

- If the Boolean formula evaluates to TRUE for a given input instance, then a current flow must be observable at a predefined nanowire. The index of this output nanowire must be constant for a given Boolean formula.

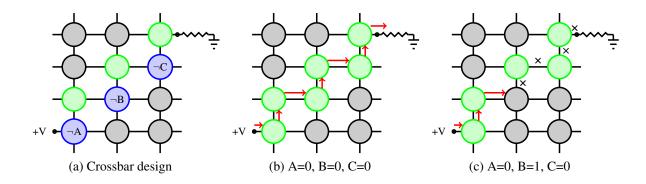

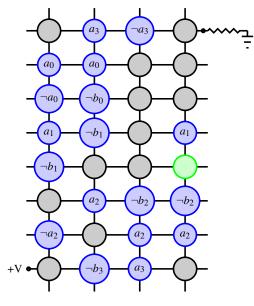

Figure 2.1: Crossbar implementing  $\neg A \land \neg B \land \neg C$  with two input instances

• If the Boolean formula evaluates to FALSE for a given input instance, then a current flow must not be observable at a predefined nanowire. The index of this output nanowire must be constant for a given Boolean formula.

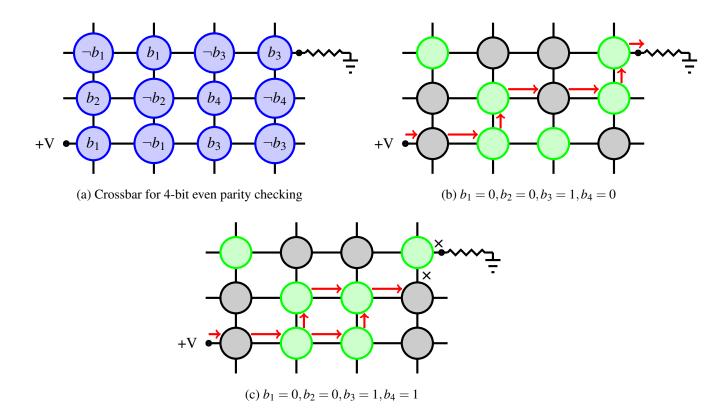

The authors of [116] have mapped Boolean formulas in the negation normal form (NNF). An example of a crossbar implementing the Boolean formula  $\neg A \land \neg B \land \neg C$  has been provided in Figure 2.1. The blue circles represent memristors which assume the value of literals, the green circles represent memristors in the ON state and the grey circles represent memristors in the OFF state. In Figure 2.1(b) and 2.1(c), the red arrows represent current flow and the crosses represent lack of current flow. However, this method produces crossbars that are very large and therefore inefficient with respect to space constraints. For this reason, the authors of [118] have leveraged the power of formal methods to synthesize compact memristors. The crossbar is synthesized as a symbolic mapping matrix, which must adhere to certain logical constraints. These constraints specify the flow-transition behavior of the crossbar, as well as its size constraints. The synthesis is achieved in a smaller number of computational steps than existing methods and produces more compact crossbars. One of the designed crossbars implements 4-bit even parity check, as shown in Figure 2.2, where the blue circles represent memristors which assume the value of literals, the green circles represent memristors in the *ON* state and the grey circles represent memristors in the *OFF* state. In Figure 2.2(b) and 2.2(c), the red arrows represent current flow and the crosses

represent lack of current flow.

Figure 2.2: Crossbar implementing 4-bit parity checking with two input instances

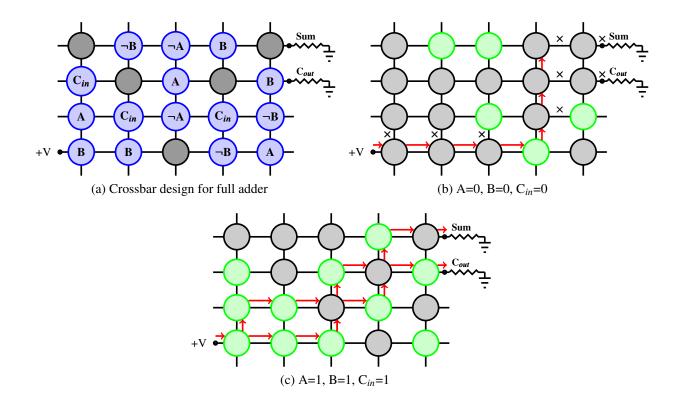

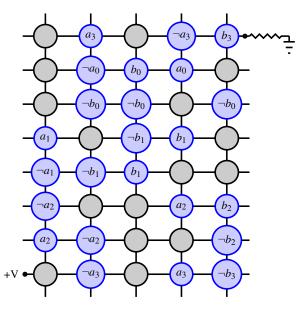

The automated synthesis of compact crossbars opened up the possibility of implementing them in hardware. In [119], a crossbar implementing a full adder has been realized. The resistive switches were implemented using a IBM 65nm 10LPe process – each device was fabricated using SiO<sub>2</sub>, TaN/Ta, electroplated Cu and HfOx. The design of the fabricated circuit is provided in Figure 2.3. The blue circles represent memristors which assume the value of literals, the green circles represent memristors in the ON state and the grey circles represent memristors in the OFF state. In Figure 2.3(b) and Figure 2.3(c), the red arrows represent current flow and the crosses represent lack of current flow. The mechanism using sneak paths has been used in [120] to perform fast Boolean matrix multiplication using crossbar circuits. A memristor is usually bi-directional, i.e., an ON memristor allows current flow through itself regardless of the terminal the flow is introduced in.

Figure 2.3: Crossbar implementing a full adder with two input instances

However, this is a property that can sometimes generate unwanted sneak paths. In such a scenario, a diode can be connected in series with the memristor to ensure that current flows in a single direction. This combined device is termed as a rectifying memristor, and they can be used to synthesize more compact crossbars that are capable of performing intensive computations [121] like Boolean matrix multiplications. This is a topic that we will explore in greater depth in some of the following sections of this document.

### **CHAPTER 3: MOTIVATION**

From the background work, we can observe that there exists a definite need to eliminate or circumvent the Von Neumann bottleneck for post-Moore's Law computing paradigms. Based on the literature review section, we are aware that there are a significant number of resistive switches that can serve as nanoscale switches to be deployed in emerging architectures for both in-memory computation and memory systems. The conjunction of these two developmental factors has yielded a number of novel research topics, ripe for excavation and exploration. The crossbar circuit topology has made its way into mainstream technological progress [122, 123]. Moreover, significant development has been made towards efficient fabrication of the crossbar circuits [124, 125, 126]. A combination of the above developments has led to the production of high-performance memory devices [127, 128] on the crossbar fabric. While all these advancements have resulted in performance and scalability improvements, the Von Neumann bottleneck has remained a persistent detractor of further gains in computing power.

One of the solutions that would effectively deal with the bottleneck is the notion of in-memory computing – the data is stored on the same physical device that performs computation on it. The principles of flow-based computing provide a novel and transformational framework to perform in-memory computing with memristor-based crossbar networks. There exist multiple problems, as outlined in the abstract, which have potential to make considerable impact upon the current state-of-the-art in this area of research. Hence, making non-trivial contributions towards the development of in-memory computation on memristor-based crossbar circuits serves as compelling motivation for this body of work.

# CHAPTER 4: AUTOMATED SYNTHESIS OF LARGE SCALE CROSSBARS WITH REDUCED ORDERED BINARY DECISION DIAGRAMS

Crossbars as abstractions

In order to synthesize crossbar designs successfully, it is inefficient and cumbersome to stick to electrical models of crossbar circuits. Hence, we to encapsulate crossbar circuits as abstractions (that can be easily manipulated to aid in synthesis procedures) as follows:

**Definition 1.** CROSSBAR A (memristor-based) crossbar is a 3-tuple  $\mathbb{C} = (\mathbb{M}, \mathbb{W}_r, \mathbb{W}_c)$  where

•  $\mathbb{M} = \begin{pmatrix} m_{11} & m_{12} & \cdots & m_{1n} \\ \vdots & \vdots & \ddots & \vdots \\ m_{l1} & m_{l2} & \cdots & m_{ln} \end{pmatrix}$  is a two-dimensional array of memristors with l rows and n columns,

where  $m_{ij} \in [0,1]$  denotes the state of the memristor (ON or OFF) connecting row i with column j.

- $\mathbb{W}_r = \{r_1, \dots, r_l\}$  is the set of horizontal nanowires such that the wire  $r_i$  provides the same input voltage to every memristor in row *i*.

- $\mathbb{W}_c = \{c_1, \dots, c_l\}$  is the set of vertical nanowires such that the wire  $c_j$  provides the same input voltage to every memristor in row *i*.

The memristor  $m_{ij} = 0$  is said to be in the high-resistance state or OFF state and  $m_{ij} = 1$  denotes a memristor in the low-resistance state or ON state.

**Definition 2.** CROSSBAR DESIGN A crossbar design  $\mathscr{D}(\mathbb{M})$  maps each memristor  $m_{ij}$  in the crossbar  $\mathbb{M}$  to one of the following: an input Boolean variable  $v_1, \dots, v_n$ , its negations  $\neg v_1, \dots, \neg v_n$  or the logical constants True or False.

For a crossbar with l rows, n columns and v different input variables, each memristor can be

mapped to 2v + 2 different values. Hence the number of possible crossbar designs is as large as  $(n \times l)^{2v+2}$ . As mentioned previously, "sneak" paths have been used as design primitives for suitable designed memristive crossbars. For a given crossbar design corresponding to a Boolean formula and a given set of values for the input variables, a current flow can be introduced in one of the nanowires. The index of this nanowire is determined by the design specifications, and is often the top or bottom row (horizontal nanowire) or the first column (vertical nanowire), of the crossbar. A non-negligible voltage is observed at the output nanowire if and only if the Boolean formula evaluates to true for the given set of inputs. Conversely, a negligible voltage is observed at the output nanowire if and only if the Boolean formula evaluates to false for the given set of inputs. The negligible and non-negligible voltage levels represent the logical constants true and false, respectively. The index of the output nanowire is once again determined by the design specifications, and it is often the top or bottom row (horizontal nanowire) of the given crossbar.

#### Binary Decision Diagrams (BDDs) and Reduced Ordered Binary Decision Diagrams (ROBDDs)

A Boolean Decision Diagram (BDD) [129, 130] is a rooted directed acyclic graph that consists of two types – terminal nodes representing the logical values 0 (for false) and 1 (for true) and non-terminal Boolean nodes labeled by Boolean variables. Each decision node has a "high" edge and a "low" edge. The high edge represents the case when the Boolean variable associated with the node has a value of 1. Similarly, the "low" edge represents the case when the Boolean variable associated with the decision variable has a value of 0. For a given value of a variable, only one of the edges from the decision variable can exist at a time. Hence, for a given set of inputs, there exists a path from the root node to one of the terminal nodes. The terminal node represents the output of the given Boolean function with respect to the given set of inputs. If a path exists from the root node to the one terminal, then the Boolean formula evaluates to false. Similarly, if a path exists from the root node to the one terminal, then the Boolean formula evaluates to true. An Ordered Binary Decision Diagram (OBDD) is a Binary Decision Diagram where the

variables appear in the same order from the root node to one of the terminal nodes, regardless of the input set that is provided to it. Variable ordering affects the size of a BDD. The "correct" or optimal variable ordering can result in a BDD of optimal size, an "incorrect" or non-optimal variable ordering can cause the size of a BDD to explode. While an optimal variable ordering is not always necessary, a good variable ordering which yields in a BDD of reasonable size is rather desirable. A Reduced Ordered Binary Decision Diagram (ROBDD) is an ordered binary decision diagram where isomorphic sub-graphs have been merged and nodes whose children are isomorphic to mean other have also been removed. The transformation of an OBDD to a ROBDD returns a decision diagram with a lower number of nodes at the different levels, or decision diagrams which have a fewer number of levels overall. The effectiveness variable ordering and reduction varies with the structure and complexity of the Boolean formula being represented by the ROBDD. Due to the fact that ROBDDs are canonical for a given function and a specific variable ordering, they have found significant applications in functional equivalence checking and functional technology mapping. A number of different libraries like CUDD [131], BuDDy, etc. exist, which facilitate ROBDD-based research and application development with greater ease.

#### Inductive mapping of ROBDDs to crossbar circuits

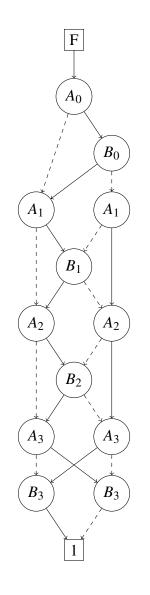

A ROBDD for a Boolean formula  $\phi$  is a directed acyclic graph  $G_{\phi}$  where the nodes are naturally divided into levels such that all outgoing edges from nodes at level *i* only connect to nodes at levels *i*+1 or higher. The subgraph  $G_{\phi}[i:j]$  of a ROBDD containing all nodes from level *i* to level *j* is mapped into a crossbar  $\mathbb{M}(G_{phi}[i:j])$  using induction.

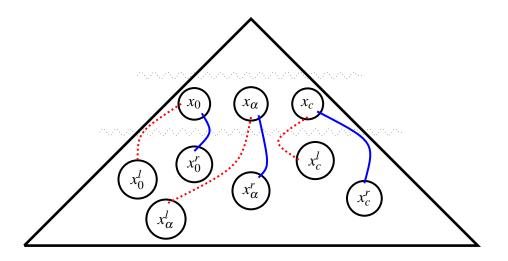

<u>Base Case</u>: The smallest entity in our design approach is a subgraph  $G_{\phi}[i:i]$  with nodes at the same  $i^{th}$  level in the ROBDD.

As shown in Figure 4.1, let a single level  $G_{\phi}[i:i]$  of a Boolean Decision Diagram contain *c* nodes  $x_0, x_1, \dots, x_c$ . Each node  $x_i$  as at most two children: if the variable *x* corresponding to the node  $x_i$

is true, the child is  $x_i^r$ . On the other hand, if the variable *x* is false, the child of the node  $x_i$  is  $x_i^l$ . The logical value of the children coupled with the logical value of the variable labeling this node produces the logical value computed by the nodes at this level.

Figure 4.1: Nodes at a single level of a ROBDD and their children

Since the nodes  $x_0^l, x_0^r, \ldots, x_c^l, x_c^r$  are at levels lower than the nodes  $x_0, x_1, \ldots, x_c$ , these nodes compute functions that are independent of the variable labeling the  $i^{th}$  level or of variables in nodes at higher levels. The single level of a Binary Decision Diagram with c nodes is mapped to a crossbar with approximately 3c rows and c columns. From there on, the induction will proceed on the number if levels H in the fragment  $G_{\phi}[i:j]$  of the Boolean Decision Diagram. The variables are assigned *TRUE (ON* memristor) or *FALSE (OFF* memristor) values on the basis of a given input instance.

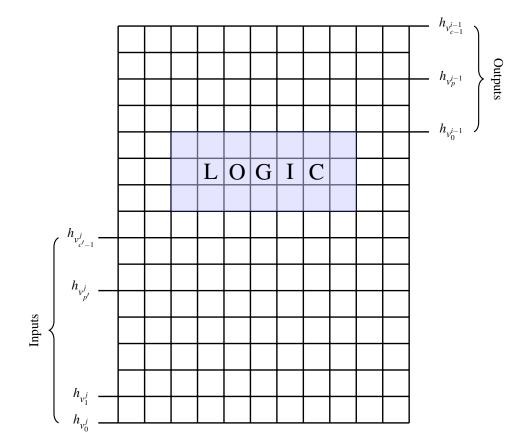

<u>Inductive Hypothesis</u>: For every subgraph  $G_{\phi}[i:j]$  of a ROBDD containing all nodes from level i to level j such that  $j \ge i$  and  $j - i \le H$ , there exists a crossbar  $\mathbb{M}(G_{\phi}[i:j])$  that contains horizontal nanowires  $h_{v_0^{i-1}}, h_{v_1^{i-1}}, \dots, h_{v_{c-1}^{i-1}}$  computing the value of the Boolean formula corresponding to the nodes  $v_0^j, v_1^j, \dots, v_{c-1}^j$  given that the values corresponding to the nodes  $v_0^j, v_1^j, \dots, v_{c'-1}^j$  are available on the corresponding input nanowires. Figure 4.2 demonstrates a crossbar that computes  $G_{\phi}[i:j]$

along with its input and output nanowires. The inductive hypothesis assumes that the subgraph  $G_{\phi}[i:j]$  can be mapped to a crossbar with the inputs (corresponding to level *j* of the ROBDD) being fed along the lower rows and the outputs (corresponding to level *i* of the ROBDD) leaving the crossbar along the higher rows.

Figure 4.2: Mapping a subgraph to a crossbar, as a basis for the inductive hypothesis

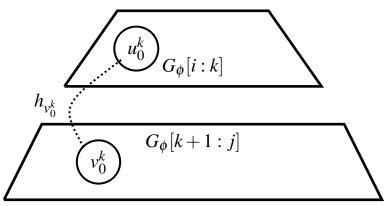

<u>Induction</u>: Consider a subgraph  $G_{\phi}[i:j]$  containing all nodes from level *i* to level *j* (*j* > *i* and j - i = H) of a ROBDD  $G_{\phi}$  for the Boolean formula  $\phi$ . First, a level *k* between *i* and *j* is chosen. The subgraph  $G_{\phi}[i:j]$  is divided into subgraphs  $G_{\phi}[i:k]$  and  $G_{\phi}[k+1:j]$  with directed edges  $(u_0^k, v_0^k), (u_1^k, v_1^k), \dots, (u_{c-1}^k, v_{c-1}^k)$  from the subgraph  $G_{\phi}[i:j]$  to  $G_{\phi}[k+1:j]$ . Similarly,  $(u_0^{i-1}, v_0^{i-1}), (u_1^{i-1}, v_1^{i-1}), \dots, (u_{d-1}^{i-1}, v_{d-1}^{i-1})$  are directed edges coming into  $G_{\phi}[i:k]$  and  $(u_0^j, v_0^j), (u_1^j, v_1^j), \dots, (u_{e-1}^{i-1}, v_{d-1}^{i-1})$  are directed edges coming out of  $G_{\phi}[k+1:j]$ .

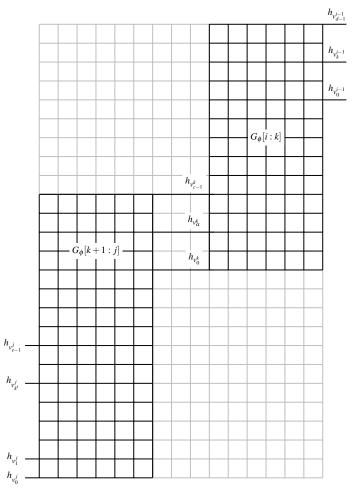

By the inductive hypothesis, for the subgraph  $G_{\phi}[k+1:j]$ , there exists a crossbar  $\mathbb{M}(G_{\phi}[k+1:j])$  that contains horizontal nanowires  $h_{v_0^k}, h_{v_1^k}, \dots, h_{v_{c-1}^k}$  computing the value of the Boolean formula corresponding to the nodes  $v_0^k, v_1^k, \dots, v_{c-1}^k$  given that the values corresponding to the nodes  $v_0^j, v_1^j, \dots, v_{e-1}^j$  are available on the corresponding input horizontal nanowires. Similarly, the the inductive hypothesis, there exists a crossbar  $\mathbb{M}(G_{\phi}[i:k])$  that contains horizontal nanowires  $h_{v_0^{i-1}}, h_{v_{1-1}^{i-1}}, \dots, h_{v_{d-1}^{i-1}}$  computing the value of the Boolean formula corresponding to the nodes  $v_0^{i-1}$ ,  $v_1^{i-1}, \dots, v_{d-1}^{i-1}$  given that the values corresponding to the nodes  $v_0^k, v_1^k, \dots, v_{c-1}^k$  are available on the corresponding to the nodes  $v_0^{i}, v_1^k, \dots, v_{d-1}^{i-1}$  given that the values corresponding to the nodes  $v_0^k, v_1^k, \dots, v_{c-1}^k$  are available on the corresponding input horizontal nanowires. As shown in Figure 4.3, the crossbar corresponding to the subgraphs  $G_{\phi}[i:j]$  can be obtained by merging smaller crossbars corresponding to the subgraphs  $G_{\phi}[k+1:j]$  and  $G_{\phi}[i:k]$  of the Boolean Decision Diagram. The lower crossbar may produce outputs in a different order than the inputs expected by the upper crossbar but permutations of rows (or columns) do not change the computation being performed by a crossbar; hence the rows of one crossbar can be rearranged to meet the desired rows of the other crossbar.

**Theorem 1.** The number of rows R(N) and the number of columns C(N) of a memristive crossbar  $\mathbb{M}(G_{\phi})$  that computes the Boolean formula  $\phi$  corresponding to a ROBDD  $G_{\phi}$  is linear in the number of nodes N of the ROBDD  $G_{\phi}$ .

*Proof.* We will show that  $R(i) \le 3i$  for all *i* using mathematical induction where *i* is the number of nodes between two levels of a ROBDD.

*Base Case:* An upper bound on the number of rows R(i) for BDDs with one node can be computed as:

- $R(|G_{True}|) \leq 3.$

- $R(|G_{False}|) \leq 3.$

- $R(|G_x|) \leq 3.$

- $R(|G_{\neg x}|) \leq 3.$

(a) The subgraphs  $G_{\phi}[i:k]$  and  $G_{\phi}[k+1:j]$  of the BDD with one of the edges  $(u_0^k, v_0^k)$ .

(b) Inductive synthesis of the crossbar for  $G_{\phi}[i:j]$  from the crossbars corresponding to subgraphs  $G_{\phi}[k+1:j]$  and  $G_{\phi}[i:k]$ . The nanowire  $h_{v_0^k}$  carries the value corresponding to node  $v_0^k$  in the crossbar for  $G_{\phi}[k+1:j]$  to the crossbar for  $G_{\phi}[i:k]$ .

Figure 4.3: Inductive synthesis of memristor crossbar circuits based on ROBDDs

Hence,  $R(1) \leq 3$ .

*Inductive Hypothesis:* Assume that  $R(i) \le 3i$  for all i < N, where *i* is the number of nodes between two levels of a ROBDD, say  $G_{\phi}[i:j]$ .

*Inductive Step:* Consider the number of rows R(N) corresponding to the number of nodes between two levels of a ROBDD, say  $G_{\phi}[i:j]$ .

$$R(N) = R(|G_{\phi}[i:j]|)$$

$$\leq R(|G_{\phi}[i:k]|) + R(|G_{\phi}[k+1:j]|) \text{ (by design of the crossbar)}$$

$$\leq 3|G_{\phi}[i:k]| + 3|G_{\phi}[k+1:j]| \text{ (by inductive hypothesis)}$$

$$= 3(|G_{\phi}[i:k]| + |G_{\phi}[k+1:j]|)$$

$$= 3N \text{ (since, } |G_{\phi}[i:k]| + |G_{\phi}[k+1:j]| = |G_{\phi}[i:j]| = N)$$

By symmetry, the number of columns C(N) is also linear in the number of nodes of the ROBDD. The identical argument is omitted for the sake of brevity.

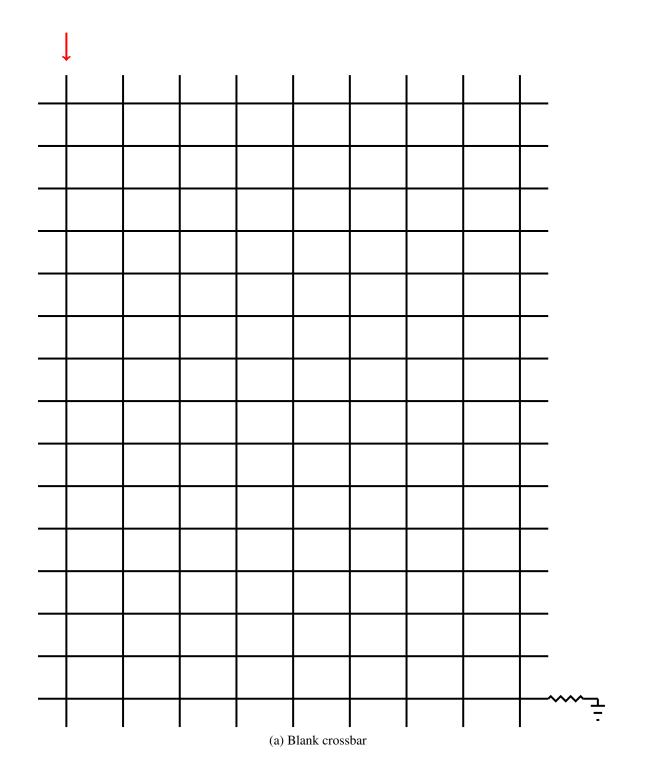

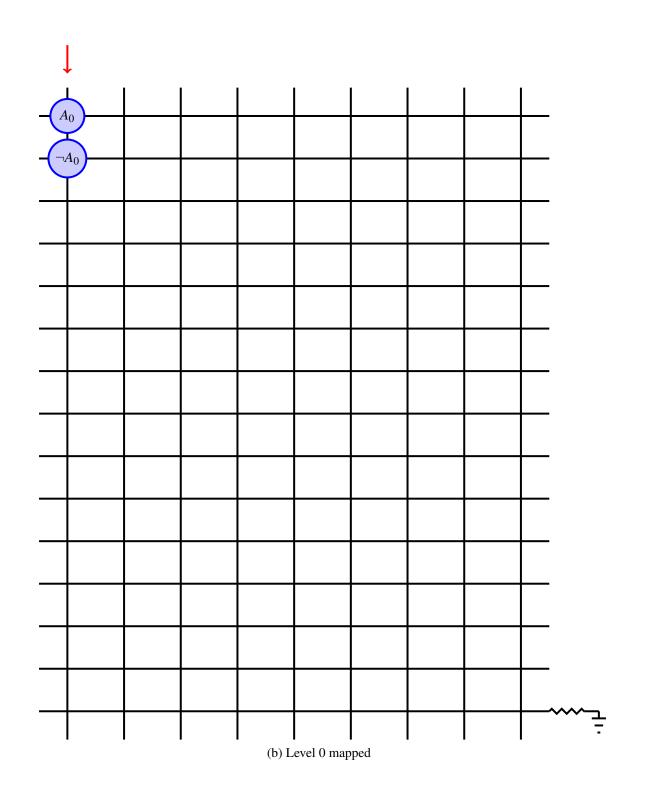

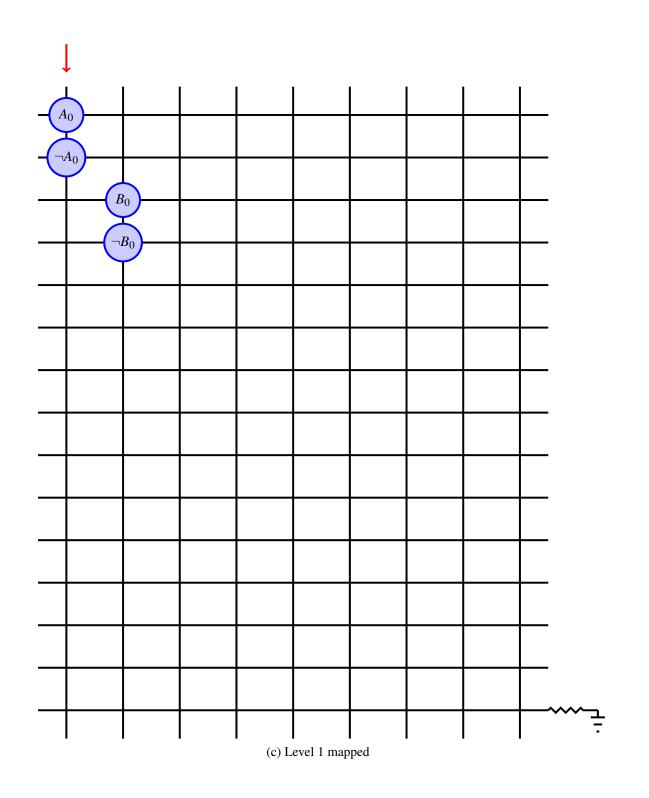

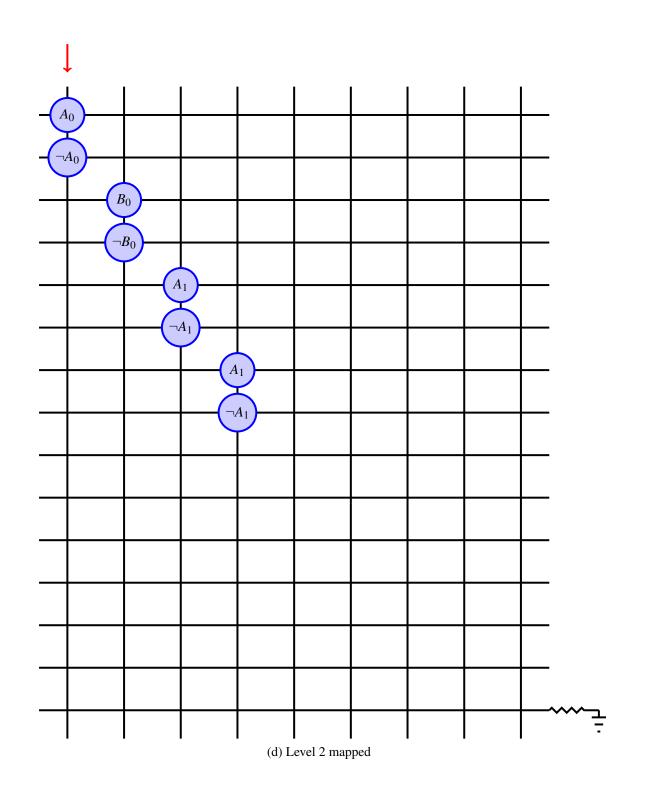

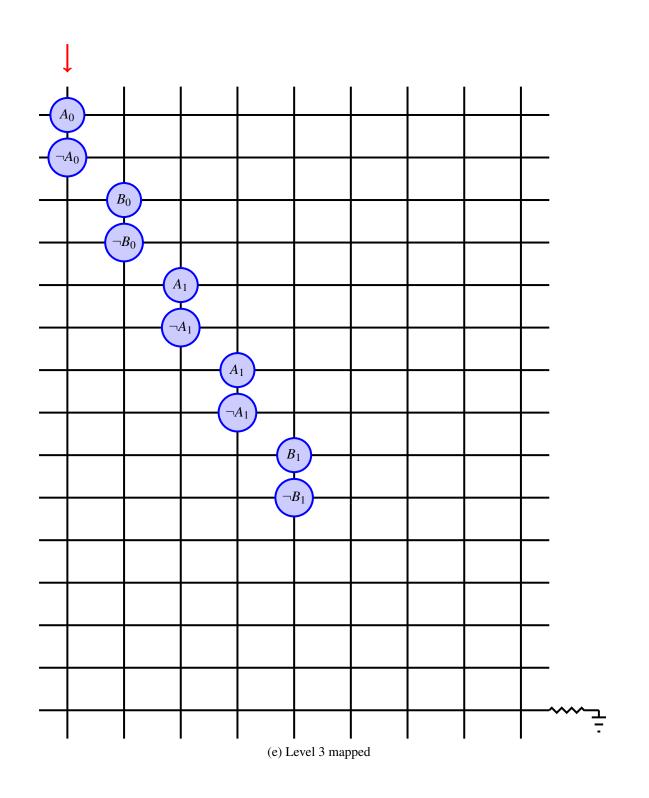

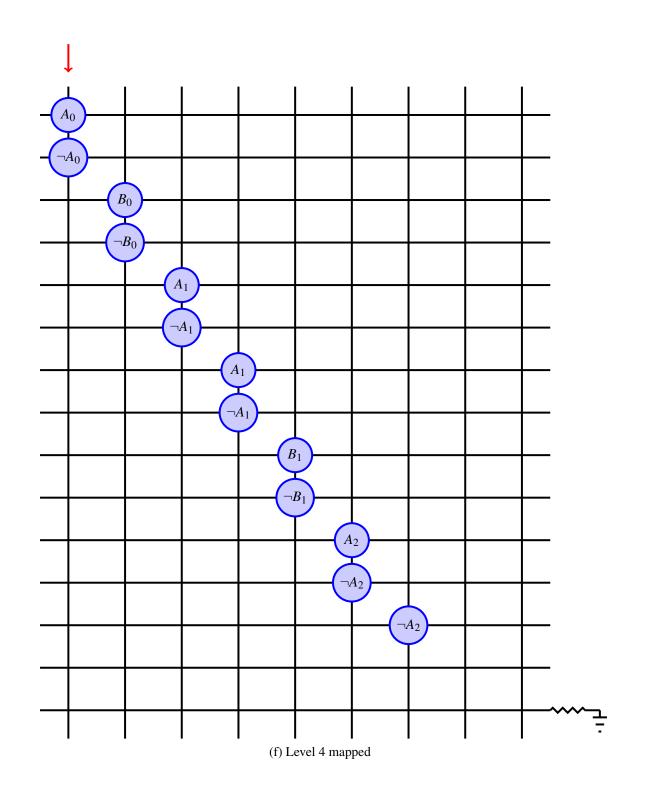

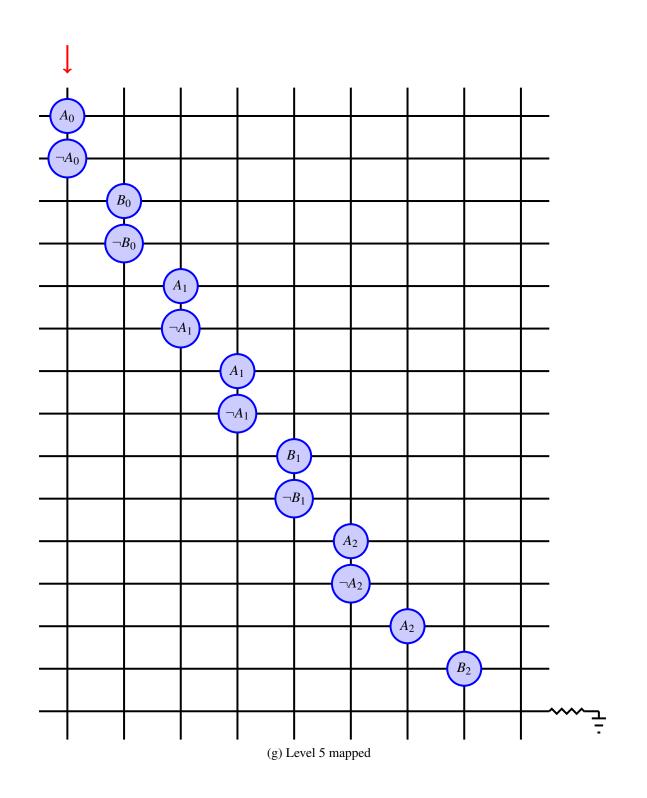

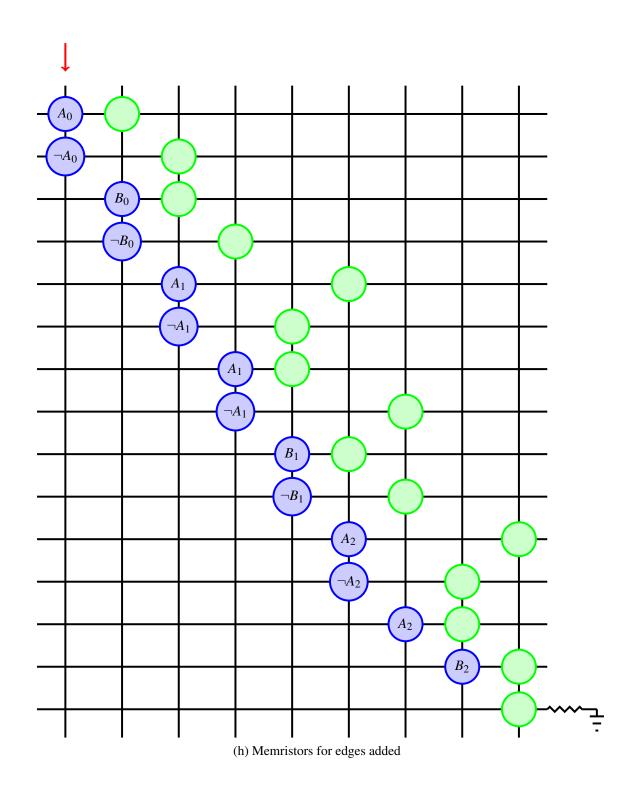

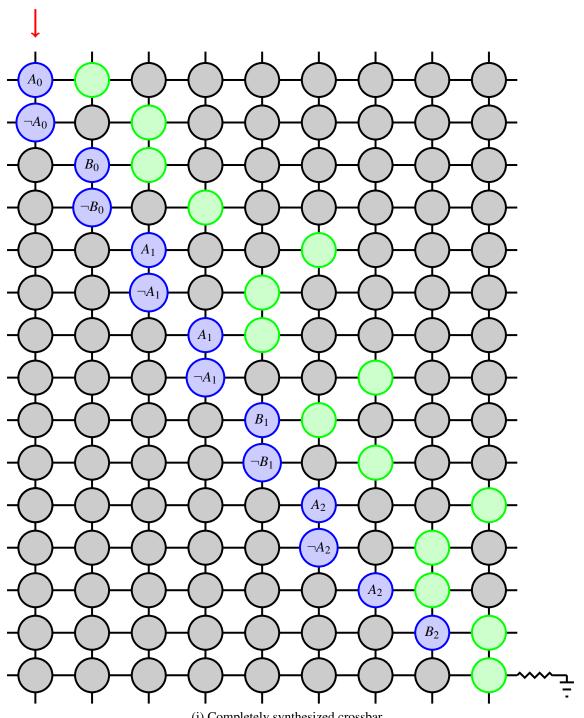

Next, we show the step-by-step mapping of a given ROBDD to a memristive crossbar circuit. In this case, the ROBDD represents the most significant bit of the  $C_{out}$  of Boolean addition between two 3-bit binary numbers, A and B. The least significant bit of the variable A is referred by  $A_0$ , the most significant bit is referred by  $A_2$ , and the middle bit is  $A_1$ . The same naming convention is followed for the variable B, as well. The ROBDD with demarcated levels is presented in Figure 4.4. In case of the crossbar, a current flow is introduced at the first column and an output flow (or lack thereof) is observed at the bottom row. The blank crossbar (without any memristors placed at the intersections of vertical and horizontal nanowires) is presented in Figure 4.5, along with the level-by-level mapping of the ROBDD to the crossbar. As can be observed, the nodes are mapped to the crossbar first, then permanently *ON* memristors are added to represent the edges between the nodes. The switches corresponding to the nodes in level 0 of the ROBDD are mapped in Figure 4.5(b).

Figure 4.4: ROBDD representing the most significant bit of 3-bit binary addition

In a similar fashion, the switches corresponding to the nodes in level 1 are added to the crossbar in Figure 4.5(c), switches corresponding to the nodes in level 2 of the ROBDD are added in Figure 4.5(c) and so on, till Figure 4.5(g), where we add the switches corresponding to the nodes in level 5 of the ROBDD. Finally, the permanently *ON* memristors corresponding to the directed edges of the ROBDD are added in Figure 4.5(h). Once these memristors have been placed, the rest of the junctions are filled with permanently *OFF* memristors, as shown in Figure 4.5(i). In this way, there exists a path from the first column to the bottom row if and only if the Boolean formula evaluates to true and the memristors are turned to the *ON* or *OFF* states corresponding to their binary values. We have presented this approach in [132].

Figure 4.5: Level-by-level mapping of ROBDD to a crossbar

## **CHAPTER 5: CROSSBAR SYNTHESIS USING MODEL COUNTING**

Synthesis of crossbars with bidirectional memristive switches

The utilization of ROBDDs helps us synthesize crossbar circuits for a large number of variables. It is also worth noting that the synthesized crossbars, while functional, are rather inefficient with respect to space constraints. Hence, the synthesis of functional and more compact crossbars makes for a worthwhile pursuit. One of such crossbars is presented in Figure 5.1. The crossbar, despite having only having a size of  $4 \times 3$  is functional, and computes the most significant bit of 2-bit binary addition.

Figure 5.1: Compact crossbar circuit for computing MSB of 2-bit binary addition

The approach for synthesizing compact crossbars driven by simulated annealing [133] is presented in Algorithm 1. In line 1, a crossbar design of size *l* rows and *n* columns is chosen randomly. Each memristor in the design is mapped to either *True*, *False*, one of the variables  $v_1, v_2, ..., v_k$  or one of the negated variables  $\neg v_1, \neg v_2, ..., \neg v_k$  using a uniform random distribution. For each crossbar design  $\mathscr{D}$ , we assume that a flow of current is injected into the bottom row (lowermost horizonAlgorithm 1: Crossbar synthesis algorithm

**Input** : Target Boolean formula  $\phi$  over variables  $\{v_1, v_2, \dots, v_k\}$ Size of crossbar  $\mathbb{C}$ : *l* rows and *n* columns Initial temperature for simulated annealing TCooling rate *c* **Output:** Crossbar design  $\mathscr{D}(\mathbb{M})$  mapping each memristor  $m_{ij} \in \mathbb{M}$  to the set {*True*, *False*,  $v_1$ , ...,  $v_k$ ,  $\neg v_1$ , ...,  $\neg v_k$ } 1  $\mathscr{D}_1 \leftarrow \text{PickRandomCrossbarDesign}(l, n, v_1, \dots, v_k)$ 2  $\mathscr{B}(\mathscr{D}_1) \leftarrow \text{BooleanFlow}(\mathscr{D}_1)$ 3  $\Delta_1 \leftarrow \text{ModelCount}(\mathscr{B}(\mathscr{D}_1) \oplus \phi)$ 4 while  $\Delta_i > 0$  do  $\mathscr{D}_{i+1} \leftarrow \operatorname{PerturbCrossbarDesign}(\mathscr{D}_i, \phi)$ 5  $\mathscr{B}(\mathscr{D}_1) \leftarrow \text{BooleanFlow}(\mathscr{D}_{i+1})$ 6  $\Delta_1 \leftarrow \text{ModelCount}(\mathscr{B}(\mathscr{D}_{i+1}) \oplus \phi)$ 7 if  $rand(0,1) < e^{-(\Delta_{i+1} - \Delta_i)/T}$  then 8  $i \leftarrow i + 1$ 9  $T \leftarrow c \times T$ 10 11 **end** 12 **Return** crossbar design  $\mathcal{D}_i$

tal nanowire) of the memristor crossbar. In line 2 of the algorithm, we symbolically compute the Boolean formula representing the values of the memristors under which a flow reaches the topmost nanowire of the crossbar and denote it by BooleanFlow( $\mathscr{D}_1$ ). Let  $r_i^{(t)}$  denote the flow value of the column *j* at time *t*. At t = 0, only the first row has flow, i.e.  $r_1^{(0)} = True$  and all other rows and columns are set to *False*. For all t > 0, the following transitions are defined for each nanowire, based on the ability of turned-on memristors to create a short-circuit between their horizontal and vertical nanowires:

$$\forall i \in \{2, \dots, n\}, r_i^{(t+1)} \iff (r_i^{(t)} \lor \bigvee_{1 \le j \le n} (m_{ij} \land c_j^{(t)}))$$

$$\forall j \in \{1, \dots, m\}, c_j^{(t+1)} \iff (c_j^{(t)} \lor \bigvee_{1 \le i \le l} (m_{ij} \land r_i^{(t)}))$$

The above transitions of the rows and columns in the crossbar can be represented using Boolean functions and described succintly using Boolean Decision Diagrams (BDDs), And-Inverter-Graphs (AIGs) or other representions.

Line 3 of the algorithm computes the approximate number of satisfiable instances  $\Delta_1$  to the Boolean formula corresponding to the symmetric difference of the target Boolean formula  $\phi$  and the formula corresponding to the computation performed by the crossbar design  $\mathcal{D}_1$ . Several competitive implementations of the approximate model counting algorithms are available – any of these are applicable to our approach, as long as the algorithm produces a count of 0 feasible models only for unsatisfiable formula [134].

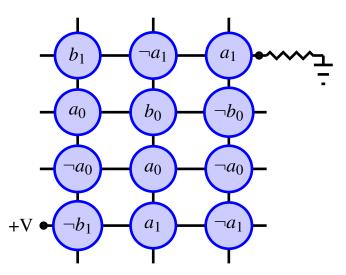

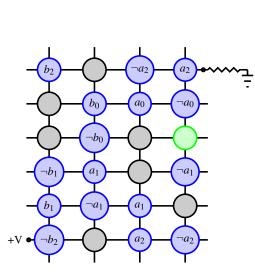

The loop in line 4 through line 12 continues to perturb the crossbar design, evaluate the function that this perturbed design computes and counts the number of satisfiable instances to the Boolean formula and the formula computed by the current crossbar design. Lines 8 through 11 are a succinct description of the simulated annealing algorithm. New crossbar designs are always accepted if they are better than the existing crossbar design. New crossbar designs that are worse than the existing crossbar design are accepted with a probability that is a function of both the quality of the designs and the current temperature of the simulated annealing algorithm. At every iteration of the loop, the temperature of the simulated annealing algorithm is slightly lowered in Line 11 of the pseudocode. At any given point in time, only a single memristor is perturbed. The probability of any given memristor being perturbed is proportional to the number of times the variable corresponding to the memristor occurs in the BDD representation of the symmetric difference between the Boolean formula and design. If a variable does not occur in the symmetric difference, it is not perturbed as the remaining error in the design in not related this variable. When the number of satisfiable instances for the symmetric difference becomes zero, the algorithm stops and reports the synthesized crossbar design. The above approach was presented in [135]. Some interesting compact crossbar designs obtained using the above approach are presented in Figure 5.2.

(a) MSB computation for 3-bit binary addition.

(b) Comparator for 4-bit binary comparison.

(c) MSB computation for 4-bit binary addition.

Figure 5.2: Compact crossbars synthesized using model counting

Synthesis of crossbars with unidirectional memristive switches

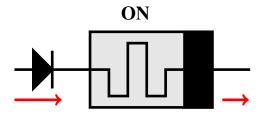

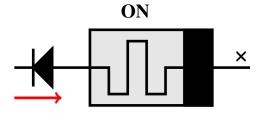

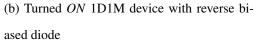

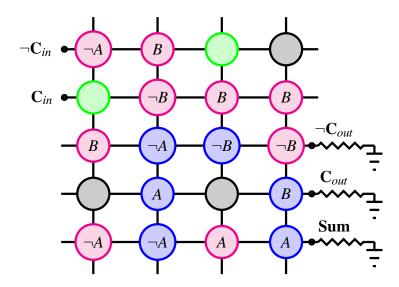

A single memristor in the *ON* state allows the flow of current through it, regardless of the terminal the current flow is introduced at. While this is an useful property, it can also give rise to paths that are entirely undesired, even within the framework of utilizing sneak paths as a computational mechanism. For this reason, it is necessary to develop and implement memristive switches that allow unidirectional current flow. This is accomplished in a reasonably simple manner in theory, by connecting a single p-n junction diode in series with a memristor – this composite device is termed as a 1D1M device, or a 1D1R device in case of resistive switches which don't necessarily exhibit memristive behavior. A pictorial representation of the fundamental working principles of these devices is provided in Figure 5.3.

(a) Turned *ON* 1D1M device with forward biased diode

(c) Turned *OFF* 1D1M device with forward biased diode

(d) Turned *OFF* 1D1M device with reverse biased diode

Figure 5.3: Switching states of 1D1M devices

The composite 1D1M devices are also termed as rectifying memristors, due to the presence of diodes. As can be observed from the above figure, a given 1D1M device only allows a current flow if and only if the memristor is turned ON and the diode is forward biased. The forward biased diode allows the flow of current through it, as opposed to a reverse biased diode which blocks the flow of current through it. Hence we can see that even if the memristor is turned ON, a current flow does not exist at the "output" terminal (terminal other than the one where the current flow is introduced) if the corresponding diode is reverse biased. Similarly, the absence of a current flow at the output terminal is noted when the diode is forward biased but the corresponding memristor is in the OFF state. Quite obviously, there is no current flow at the output terminal if the memristor is noted well.

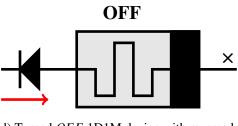

The usage of 1D1M devices empowers us to make an attempt to solve the Feynman Grand Prize challenge. The approach is presented in [136]. The Feynman Grand Prize offered by the Foresight Institute requires the design, construction and demonstration of a nanoscale digital computing device capable of performing 8-bit addition in a cube of edge length 50nm. Assuming that the device is being created using nanoscale memristors of size 3nm [137] and the inter-memristor gap is only 1nm, the 8-bit adder design can still only use crossbars of size  $12 \times 12$ . Such a compact implement tation was previously not possible, including the approaches mentioned in the earlier sections of this document. Intuitively, the next step towards the solution would be to utilize a 3-dimensional stack of nanoscale memristor crossbars. For the sake of simplicity in fabrication, it is necessary for the different layers in the stack to have limited and structured interactions. Ideally, such interactions between different layers can be accomplished by using external connections among the layers. Each crossbar layer can operate as a single full adder circuit, and eight such crossbar layers can be stacked on top of each other. Each crossbar layer in the stack needs to implement a fulladder circuit within an area of 50nm×50nm. The 3-D stacked crossbar has a limited number of connections between the different layers. The design of a single crossbar is entirely modular, and computes the sum, the carry-out and the negation of the carry-out for 1-bit Boolean addition. The design of a layer is shown in Figure 5.4.

Figure 5.4: A crossbar circuit computing the Sum,  $C_{out}$  and  $\neg C_{out}$  of 1-bit binary addition