### University of Central Florida

## **STARS**

**Electronic Theses and Dissertations**

2011

# A Sustainable Autonomic Architecture for Organically Reconfigurable Computing Systems

Rashad S. Oreifej University of Central Florida

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Oreifej, Rashad S., "A Sustainable Autonomic Architecture for Organically Reconfigurable Computing Systems" (2011). *Electronic Theses and Dissertations*. 6650. https://stars.library.ucf.edu/etd/6650

# A SUSTAINABLE AUTONOMIC ARCHITECTURE FOR ORGANICALLY RECONFIGURABLE COMPUTING SYSTEMS

by

## RASHAD S. OREIFEJ B.S. UNIVERSITY OF JORDAN, 2000 M.S. UNIVERSITY OF CENTRAL FLORIDA, 2006

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Summer Term 2011

Major Professor: Ronald F. DeMara

© 2011 Rashad S. Oreifej

#### **ABSTRACT**

A Sustainable Autonomic Architecture for Organically Reconfigurable Computing System based on SRAM Field Programmable Gate Arrays (FPGAs) is proposed, modeled analytically, simulated, prototyped, and measured. Low-level organic elements are analyzed and designed to achieve novel self-monitoring, self-diagnosis, and self-repair organic properties. The prototype of a 2-D spatial gradient Sobel video edge-detection organic system use-case developed on a XC4VSX35 Xilinx Virtex-4 Video Starter Kit is presented. Experimental results demonstrate the applicability of the proposed architecture and provide the infrastructure to quantify the performance and overcome fault-handling limitations. Dynamic online autonomous functionality restoration after a malfunction or functionality shift due to changing requirements is achieved at a fine granularity by exploiting dynamic Partial Reconfiguration (PR) techniques.

A Genetic Algorithm (GA)-based hardware/software platform for intrinsic evolvable hardware is designed and evaluated for digital circuit repair using a variety of well-accepted benchmarks. Dynamic bitstream compilation for enhanced mutation and crossover operators is achieved by directly manipulating the bitstream using a layered toolset. Experimental results on the edge-detector organic system prototype have shown complete organic online refurbishment after a hard fault. In contrast to previous toolsets requiring many milliseconds or seconds, an average of 0.47 microseconds is required to perform the genetic mutation, 4.2 microseconds to perform the single point conventional crossover, 3.1 microseconds to perform Partial Match Crossover (PMX) as well as Order Crossover (OX), 2.8 microseconds to perform Cycle Crossover (CX),

and 1.1 milliseconds for one input pattern intrinsic evaluation. These represent a performance advantage of three orders of magnitude over the JBITS software framework and more than seven orders of magnitude over the Xilinx design flow. Combinatorial Group Testing (CGT) technique was combined with the conventional GA in what is called CGT-pruned GA to reduce repair time and increase system availability. Results have shown up to 37.6% convergence advantage using the pruned technique.

Lastly, a quantitative stochastic sustainability model for reparable systems is formulated to evaluate the *Sustainability* of FPGA-based reparable systems. This model computes at designtime the resources required for refurbishment to meet mission availability and lifetime requirements in a given fault-susceptible missions. By applying this model to MCNC benchmark circuits and the Sobel Edge-Detector in a realistic space mission use-case on Xilinx Virtex-4 FPGA, we demonstrate a comprehensive model encompassing the inter-relationships between system sustainability and fault rates, utilized, and redundant hardware resources, repair policy parameters and decaying reparability.

#### ACKNOWLEDGMENTS

It is a pleasure to thank those who made this dissertation possible and truly believed in me the last few years.

I would like to express my deepest gratitude to my advisor, Dr. Ronald DeMara, for his exceptional guidance, help, valuable time, and advice in providing me with the needed research grounds to build on, and for keeping me always on the right track.

I would like to thank my respectful committee members; Drs. Samuel Richie, Jun Wang, and Mansooreh Mollaghasemi for their valuable input, discussions, and generous effort in enhancing this dissertation.

I would like to thank my friends and colleagues for their sincere and insightful support and advice. I would also like to thank my parents, sisters and brother for their unremitting love, and support they surrounded me with to fulfill my ambitions.

Finally, I would like to thank my precious wife for her understanding, encouragement, and unconditional care and love, and for truly being my best support in the good and bad times.

The research presented in this dissertation was supported in part by NASA Intelligent Systems NRA Contract NNA04CL07A and by Defense Advanced Research Projects Agency (DARPA) SBIR topic SB072-009 Contract W31P4Q-08-C-0168.

# TABLE OF CONTENTS

| LIST O | F FIGURES                  |                                              | viii        |

|--------|----------------------------|----------------------------------------------|-------------|

| LIST O | FTABLES                    |                                              | x           |

| СНАРТ  | ER 1: ID                   | ENTIFICATION AND SIGNIFICANCE OF THE PROBLEM | <i>A</i> 12 |

| 1.1.   | Need for S                 | Sustainable Systems                          | 12          |

| 1.2.   | Potential f                | or Evolvable Hardware                        | 15          |

| 1.3.   | Self-x Pro                 | perties: An Organic Computing Vision         | 17          |

| 1.4.   | Contributi                 | ons of Dissertation                          | 20          |

| СНАРТ  | ER 2: RE                   | ELATED WORK                                  | 24          |

| 2.1.   | Evolution                  | of Digital Circuit Design and Repair Tasks   | 24          |

| 2.2.   | Organic Computing Concepts |                                              |             |

| 2.3.   | Sustainability Analysis    |                                              | 33          |

|        | 2.3.1.                     | Need for Sustainability Analysis             | 34          |

|        | 2.3.2.                     | SRAM-based Fault Modeling                    | 37          |

| СНАРТ  | ER 3: MI                   | ULTI-LAYER HIGH-LONGEVITY ARCHITECTURE       | 42          |

| 3.1.   | System Ar                  | chitecture                                   | 42          |

| 3.2.   | Organic L                  | ayer Design and Implementation               | 48          |

|        | 3.2.1.                     | Organic Layer Architecture                   | 48          |

|        | 3.2.2.                     | Intrinsic Evolutionary Repair Platform       | 56          |

| 3.3.   | Summary                    |                                              | 67          |

| СНАРТ  | ER 4: OF                   | RGANIC SELF-HEALING EXPERIMENTAL RESULTS     | 68          |

| 4.1.   | Video Edg                  | ge-Detection Use-Case on Organic Layer       | 68          |

| 4.2.                                                    | Evolut                                       | tionary Design and Repair Platform                 | 78  |  |

|---------------------------------------------------------|----------------------------------------------|----------------------------------------------------|-----|--|

| CHAPTER 5: CGT-PRUNED REPAIR TECHNIQUE                  |                                              | CGT-PRUNED REPAIR TECHNIQUE                        | 94  |  |

| 5.1.                                                    | Group Testing Based Fault Location Procedure |                                                    |     |  |

| 5.2.                                                    | CGT-Pruned Expedited Genetic Algorithm       |                                                    |     |  |

| 5.3.                                                    | Experiments                                  |                                                    |     |  |

| 5.4.                                                    | Result                                       | 101                                                |     |  |

|                                                         | 5.4.                                         | 1. Fault Location Using CGT Algorithm              | 101 |  |

|                                                         | 5.4.                                         | 2. Design in the Presence of Fault                 | 102 |  |

|                                                         | 5.4.                                         | 3. Repair                                          | 103 |  |

| CHAPTER 6: A NOVEL FRAMEWORK FOR MISSION SUSTAINABILITY |                                              |                                                    | 108 |  |

| 6.1.                                                    | Sustai                                       | nability Model                                     | 108 |  |

|                                                         | 6.1.                                         | 1. Combining Multiple Faults                       | 116 |  |

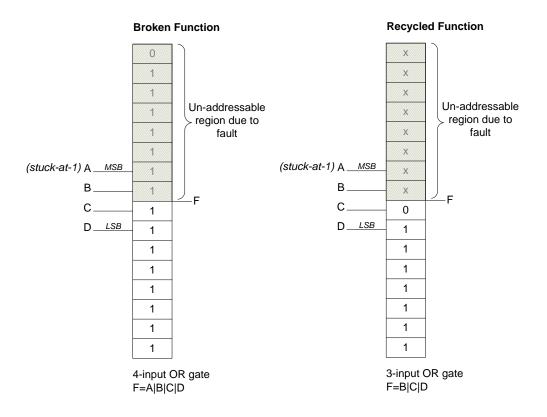

|                                                         | 6.1.                                         | 2. Resource Recycling                              | 117 |  |

|                                                         | 6.1.                                         | 3. Reparability and its Relation to Sustainability | 119 |  |

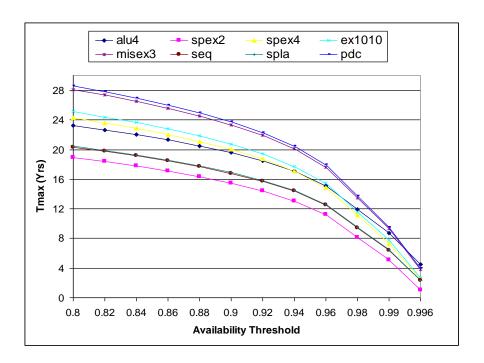

| 6.2.                                                    | MCNO                                         | C Benchmarks Case Study                            | 123 |  |

| 6.3.                                                    | Sustai                                       | nability of a Realistic Mission Use-Case           | 134 |  |

| CHAPT                                                   | ER 7:                                        | CONCLUSION                                         | 141 |  |

| 7.1.                                                    | Techn                                        | ical Summary                                       | 141 |  |

| 7.2.                                                    | Future                                       | e Work                                             | 144 |  |

| APPENI                                                  | DEX A:                                       | AES AND FES USE-CASES                              | 147 |  |

| APPENI                                                  | DEX B:                                       | ORGANIC-COGNITIVE COMMUNICATION PROTOCOL           | 152 |  |

| APPENDEX C: FPGA HARDWARE FAILURE RATES                 |                                              |                                                    |     |  |

| LIST OF REFERENCES                                      |                                              |                                                    |     |  |

# LIST OF FIGURES

| Figure 1. Autonomous-System-on-a-Chip architecture [22].                                 | . 31 |

|------------------------------------------------------------------------------------------|------|

| Figure 2. The Bathtub Curve [73]                                                         | . 41 |

| Figure 3. Soar-Longevity Conceptual Architecture                                         | . 43 |

| Figure 4. Organic Layer Architecture                                                     | . 49 |

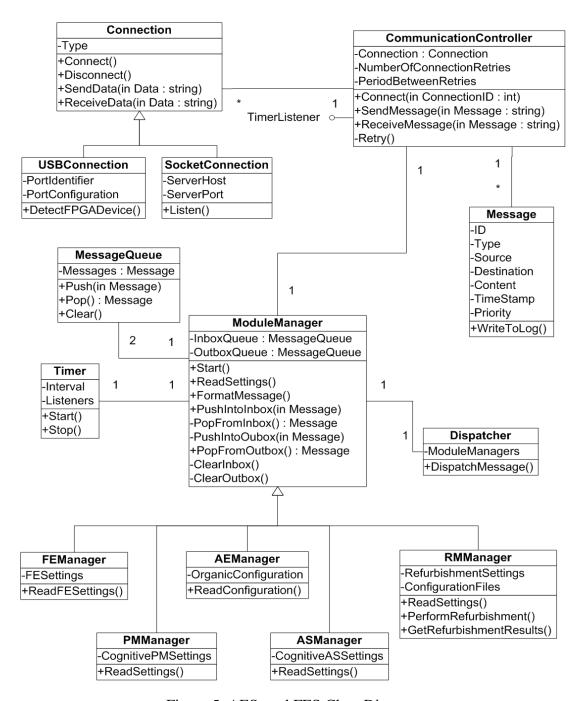

| Figure 5. AES and FES Class Diagram                                                      | . 50 |

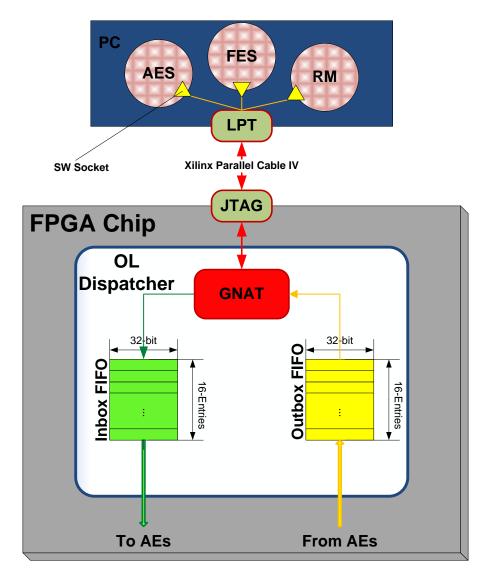

| Figure 6. Organic Layer Dispatcher Architecture                                          | . 52 |

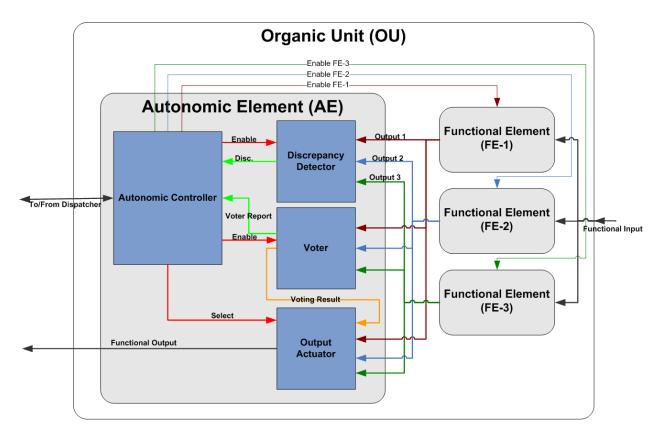

| Figure 7. Organic Unit Architecture                                                      | . 54 |

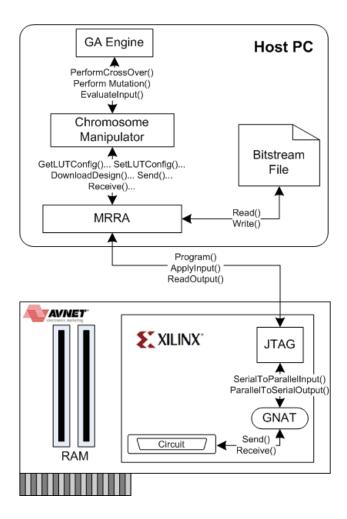

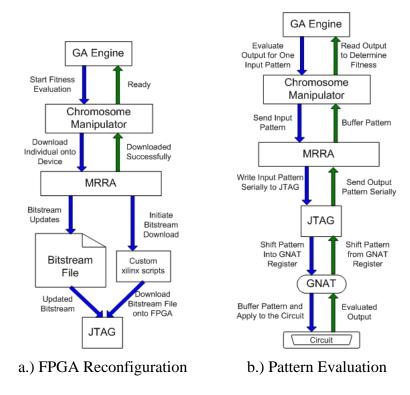

| Figure 8. Intrinsic Evolution Platform                                                   | . 57 |

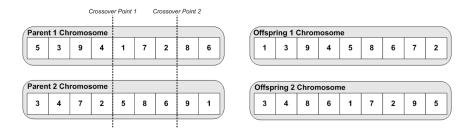

| Figure. 9. Partially Matched Crossover (PMX)                                             | . 60 |

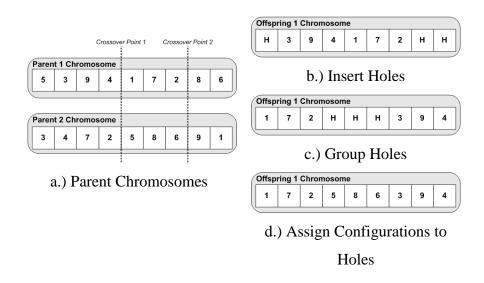

| Figure 10. Order Crossover (OX)                                                          | . 61 |

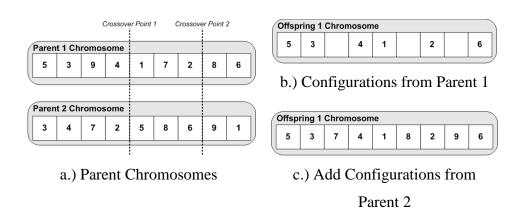

| Figure 11. Cycle Crossover (CX)                                                          | . 62 |

| Figure 12. Initialization: Obtain configuration from .bit File                           | . 65 |

| Figure 13. Fitness Evaluation: Performed in two phases a and b.                          | . 66 |

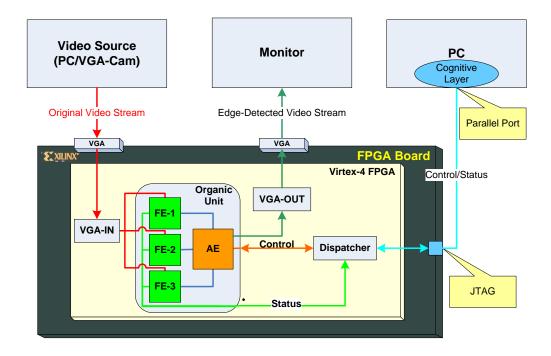

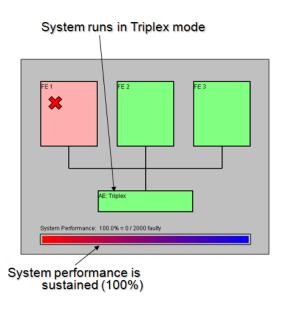

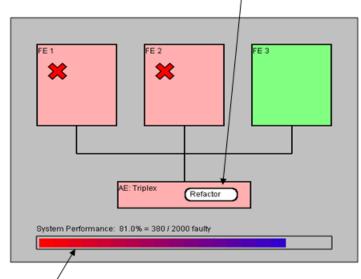

| Figure 14. Video edge-detection use-case.                                                | . 70 |

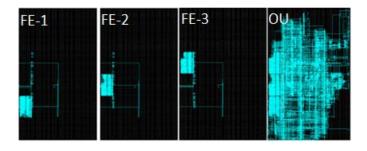

| Figure 15. FE-PR and Entire OU on FPGA Fabric                                            | . 71 |

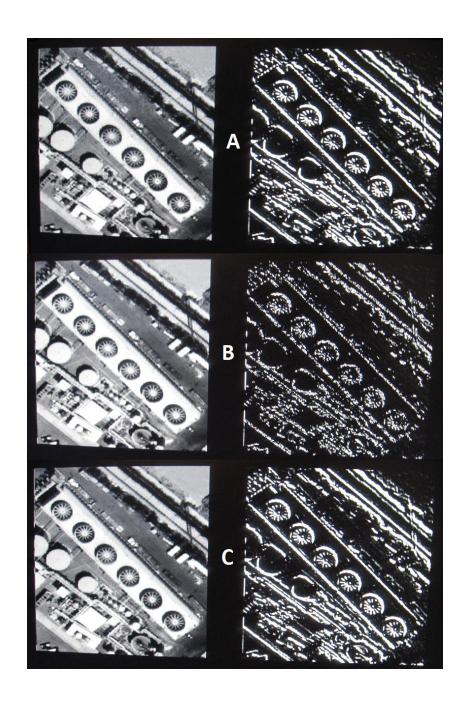

| Figure 16. Edge-detection Snap. A: Fault Free/Single Fault, B: Faulty and C: Refurbished | . 76 |

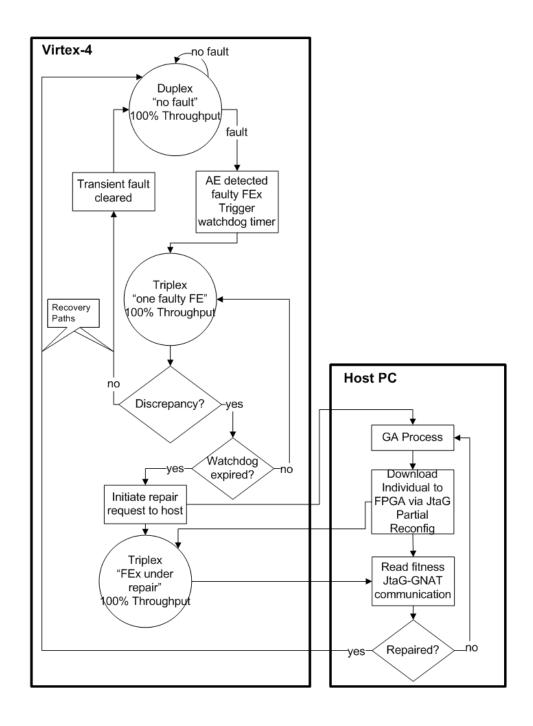

| Figure 17. Self-Repair Flow Diagram                                                      | . 77 |

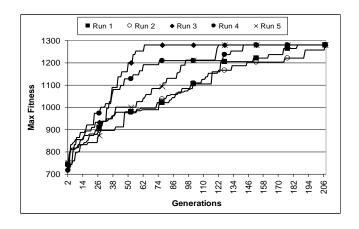

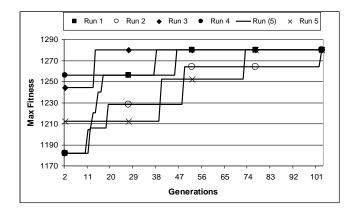

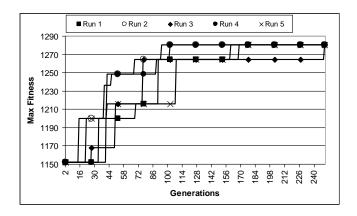

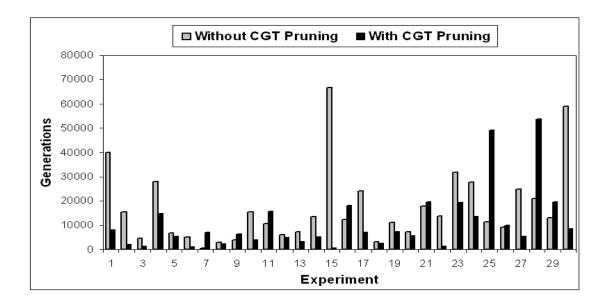

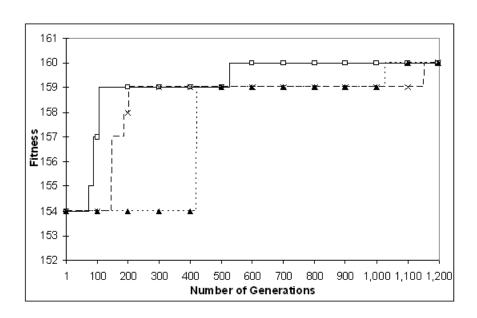

| Figure 18. Unseeded Design GA Runs                                                       | . 91 |

| Figure 19. Seeded Design GA Runs                             | 91                                          |

|--------------------------------------------------------------|---------------------------------------------|

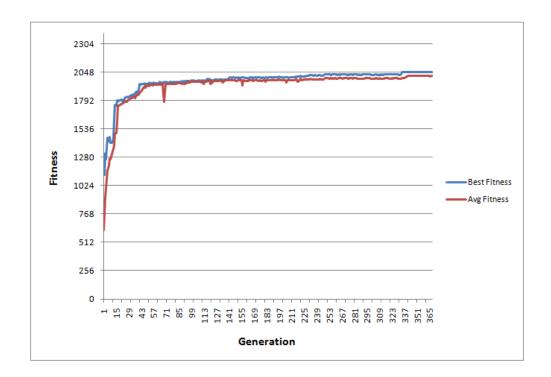

| Figure 20. Repair GA Runs                                    | 92                                          |

| Figure 21. Sobel Edge-Detector Refurbishment Eve             | olution Progress93                          |

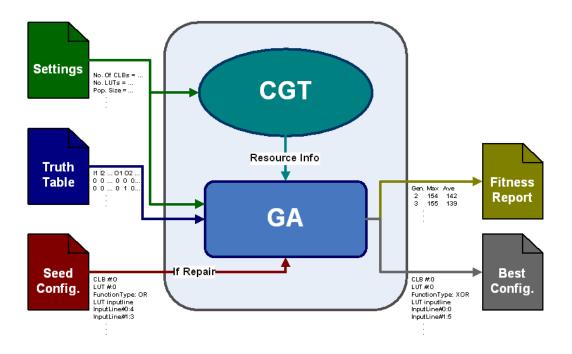

| Figure 22. Genetic Algorithm Simulator                       | 96                                          |

| Figure 23. CGT-pruned Genetic Algorithm Repair.              | 99                                          |

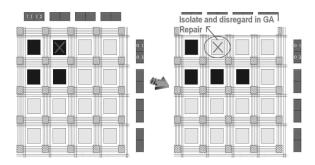

| Figure 24. Repair Progress: CGT-pruned vs. Conv              | entional GA104                              |

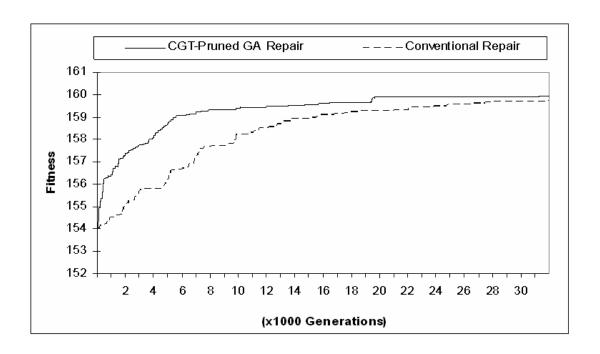

| Figure 25. CGT-pruned vs. Conventional GA Repo               | air105                                      |

| Figure 26. Three Fast Runs of the CGT-pruned GA              | Repair106                                   |

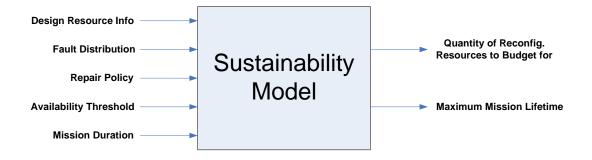

| Figure 27. Sustainability Model Functional Block I           | Diagram109                                  |

| Figure 28. Resource Recycling                                | 118                                         |

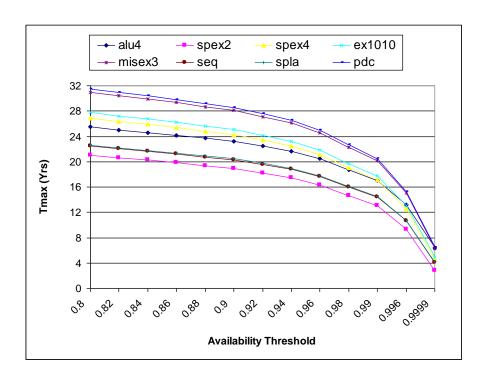

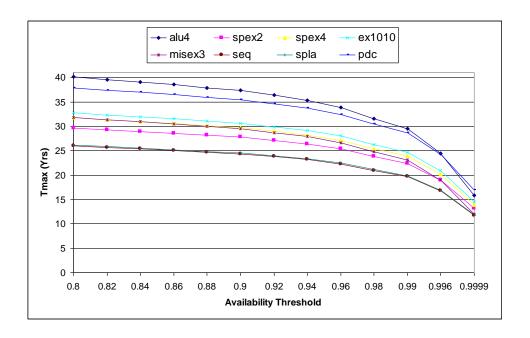

| Figure 29. MCNC $T_{max}$ vs. Availability (Conservat        | ive, QOR: 100%, Simplex)127                 |

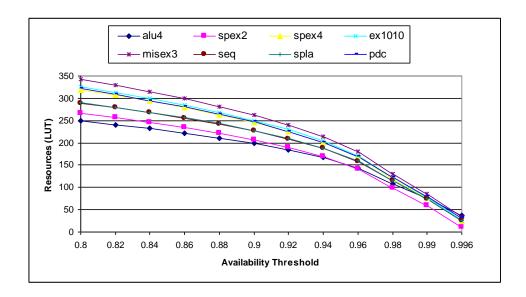

| Figure 30. Resource Required for Refurbishment (             | Conservative, QOR: 100%, Simplex) 128       |

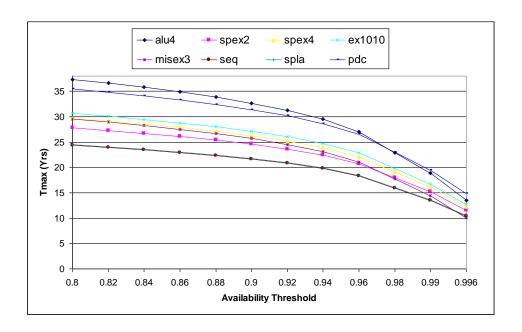

| Figure 31. MCNC Benchmarks T <sub>max</sub> versus Availal   | bility (Conservative, 100% QOR, RARS) 130   |

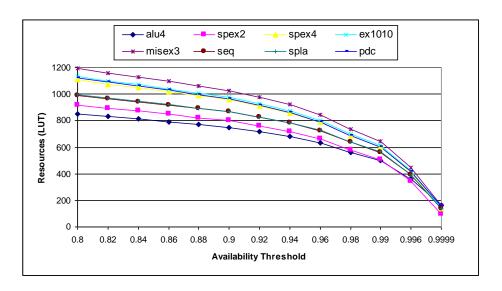

| Figure 32. Resource Required for Refurbishment (             | Conservative, 100% QOR, RARS) 131           |

| Figure 33. MCNC Benchmarks T <sub>max</sub> versus Availal   | bility (Conservative, QOR: 95%, Simplex)133 |

| Figure 34. MCNC T <sub>max</sub> versus Availability (Conser | evative, 95% QOR, RARS)134                  |

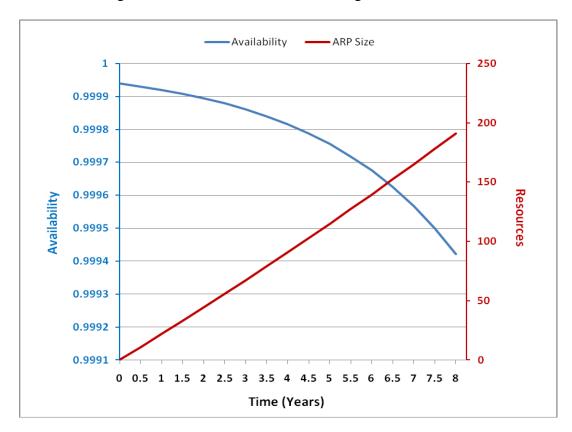

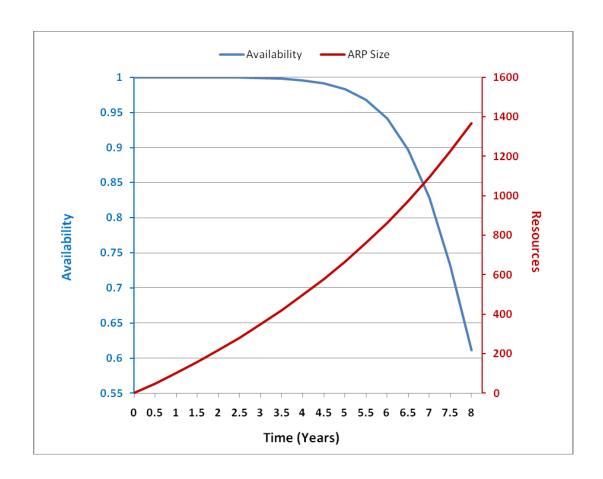

| Figure 35. Sobel Edge-detector Availability and Al           | RP Consumption (Conservative) 137           |

| Figure 36. Sobel Edge-detector Availability and Al           | RP Consumption (Pessimistic)                |

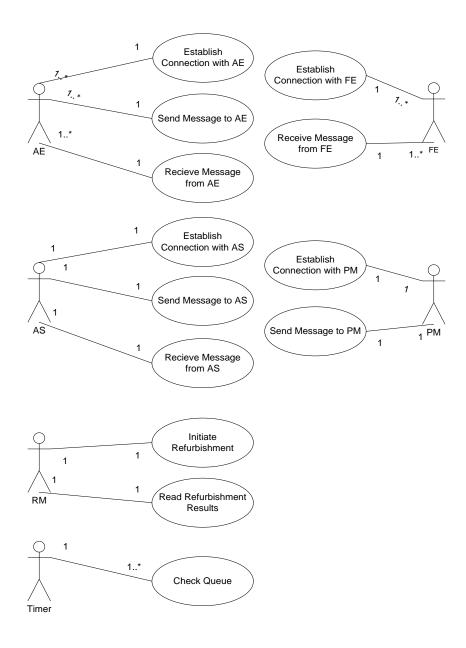

| Figure 37. AES Use-Case Diagram                              |                                             |

# LIST OF TABLES

| Table 1. SRAM-Based FPGA Fault Characteristics                                | 39  |

|-------------------------------------------------------------------------------|-----|

| Table 2. Innovative aspects of the Soar-Longevity approach.                   | 45  |

| Table 3. AES and FES Class Description                                        | 51  |

| Table 4. Fault Injection DIP Switches                                         | 71  |

| Table 5. Use-case Testing Scenarios                                           | 72  |

| Table 6. GA Parameters                                                        | 79  |

| Table 7. Sobel Edge-detector Configuration Times in Various Technologies      | 84  |

| Table 8. Experimental Results Summary for Single Point Crossover and Mutation | 85  |

| Table 9. Experimental Results Summary for PMX and Mutation                    | 86  |

| Table 10. Experimental Results Summary for OX and Mutation                    | 87  |

| Table 11. Experimental Results Summary for CX and Mutation                    | 88  |

| Table 12. GA Operators Timing (seconds)                                       | 90  |

| Table 13. GA Parameters                                                       | 100 |

| Table 14. Design of a 3-bit x 2-bit Multiplier in the Presence of a Fault     | 102 |

| Table 15. Repair of a 3-bit x 2-bit Multiplier                                | 103 |

| Table 16. MCNC Benchmark Circuits on Xilinx Virtex-4 xc4vsx35 FPGA            | 123 |

| Table 17 ARP-based GA Parameters                                              | 125 |

| Table 18. MCNC Benchmark Circuits ARP-based GA Reparability Decay (Conservative)           | 126 |

|--------------------------------------------------------------------------------------------|-----|

| Table 19. MCNC Benchmark Circuits ARP-based GA Reparability Decay (Pessimistic)            | 126 |

| Table 20. ARP-based GA Evolution Results                                                   | 132 |

| Table 21. RARS Sobel Edge-Detector with ARP-based GA Sustainability Results (Conservation) | ,   |

| Table 22. RARS Sobel Edge-Detector with ARP-based GA Sustainability Results (Pessimis      |     |

| Table 23. Actors Interacting with AES                                                      | 148 |

| Table 24. AES and FES Use Cases                                                            | 148 |

| Table 25. AES and FES Class Description                                                    | 151 |

| Table 26. Component Interactions                                                           | 153 |

| Table 27. FES Connection Protocol                                                          | 154 |

| Table 28. AES Connection Messages                                                          | 155 |

| Table 29. AES Connection Messages                                                          | 156 |

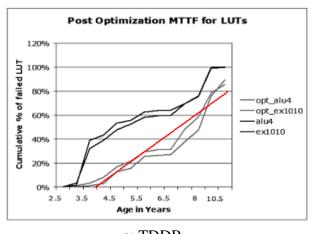

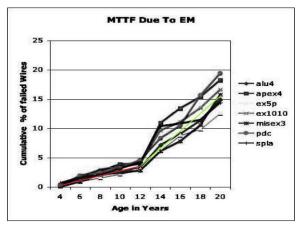

| Table 30. Detail of TDDB Lifetime in Years of Each Device [72]                             | 166 |

| Table 31. 90nm FPGA MTTF [71]                                                              | 167 |

# CHAPTER 1: IDENTIFICATION AND SIGNIFICANCE OF THE PROBLEM

Attaining high availability, reliability and fault tolerance for digital systems have long been recognized as a crucial non-functional requisite for mission critical applications. This significance is further amplified in systems such as deep space and satellite systems. Those systems target particularly sensitive missions and hence safety and security come first on top of the priority list. Additionally, the cost, complexity, and restricted visibility associated with such systems tend to be quite significant, consequently, *longevity* becomes a highly sought after objective. This chapter introduces the problem at hand, sheds some light on the approaches followed herein to tackle the problem and highlights the contributions of this work.

#### 1.1. Need for Sustainable Systems

Deep space missions encounter a very harsh operating environment due to radiation, terrestrial particles, temperature and pressure stresses, background noise, and immense electromagnetic fields. Such a deployment environment is inevitably one of the most fault-prone environments digital systems could be deployed into. Moreover, the limited possibilities to intervene at the incident of a failure make a self-restoration capability after upsets an extremely imperative characteristic to have, and the sustained spaceborne operation thus far, an increasingly challenging problem to solve.

Autonomous systems present an attractive space application as they aim to carry out complex tasks in harsh and more importantly dynamic and uncertain environments. Their capacity of fault tolerance and self-refurbishment grows in importance as the mission criticality and duration increases and as the environment becomes out of control and expectancy.

SRAM-based FGPAs, like any semiconductor devices, are subject to hardware faults. These faults could be soft faults which are transient or persistent Single Event Upsets (SEU) [1-7], or hard permanent faults [8-14]. Details on FPGA faults are identified and discussed in the following chapter. SEUs primarily affect storage elements and since FGPAs are built up from memory cells, historically, SEUs have received significant attention. However, as technology advances towards smaller nanoscale devices, systems exhibit appealing characteristics of high densities, low power, smaller size and weight. Yet, technology advances introduce increased undesirable fault susceptibility. In addition to manufacturing defects, nano-electronic devices are expected to experience a high occurrence of runtime faults [15]. This trend deprecates traditional fault tolerance approaches and promotes autonomous innovative ones.

FPGA repair mechanisms have been excessively explored. Repair techniques range from static approaches involving simple spare replacement to highly sophisticated dynamic heuristics. Despite the variety of these approaches, they all share a fundamental common goal of functionality restoration among other characteristics such as latency, redundancy, complexity, adaptability, coverage and sustainability.

Regardless of the repair approach utilized, spare resources provide flexible capacity to replace broken ones. Being dynamically reconfigurable at runtime, FGPAs enable the spare granularity to miniaturize from modular redundancy to reconfigurable resource redundancy such as Lookup Tables (LUT). The amount of unutilized (spare) reconfigurable resources the mission should carry to sustain through the targeted period is a problem to resolve. This group of unutilized resources is referred to herein by the *Amorphous Resource Pool* (ARP). A primary concern when doing online refurbishment is the Mean Time To Repair (MTTR). The lower the MTTR drops, the higher the system availability becomes. Depending on the mission requirements, there is a threshold of MTTR after which the mission falls below the acceptable availability level and hence fails. As mission progresses, cumulative faults likelihood at best remains flat, but nearly universally increases monotonically. It is anticipated that repair complexity becomes increasingly challenging. Time-to-refurbish is anticipated to increase as more parts fail. One of the main questions to answer becomes: What is the expected duration of a mission with probability of success is greater than an acceptable threshold? More specifically, how can a system sustain its functionality within planned mission availability and lifetime specifications when operating in a failure-prone ecosystem?

A *sustainable system* is hereby defined as one that is sufficiently capable of achieving mission objectives under specified ranges of varying conditions within a fault-susceptible deployment environment. Unbounded survival under degrading conditions can not be possible and hence it is fallacious to attempt assessing system's sustainability for realistic missions over an infinite time interval. A more useful definition of a sustainable system hence becomes: a system capable to operate without substantial functional depreciation throughout its expected lifetime enabled by a

particular likely finite regeneration strategy. In the electronic systems' context however, the system is said to be sustainable if it is capable of handling imminent failures throughout its lifetime by taking the actions necessary to maintaining the desired performance minimum threshold.

#### 1.2. Potential for Evolvable Hardware

Harsh operating environments, manufacturing defects, and component aging are contributing causes of hardware faults that make sustained availability and performance requirements difficult. Many hardware reliability approaches have been proposed in the literature such as fault avoidance, design margin, modular redundancy, and fault refurbishment [16]. Fault avoidance-based design approaches aim to avoid possible faults that could occur at run time. Such approaches usually impose minimal size, weight, and power overheads. Meanwhile, design margin approaches rely on an increased number of redundant system components and capabilities to enhance reliability by designing with a margin for fault tolerance.

Despite the advantages of the above approaches, anticipating all the possible faults at design-time may not only be impractical, but also not adaptive to dynamic deployment environments such as space. On the other hand, modular redundancy approaches utilize multiple identical modules each of which is capable of delivering the desired functionality. These approaches increase size, weight, and power consumption. Additionally, the recovery capacity of these approaches is limited by the number and granularity of the available redundant modules.

Fault refurbishment approaches, such as the proposed approach herein, offer a very competitive option because of the high recovery capacity and adaptability to unforeseen conditions. However, fault refurbishment is challenging due to the complexity involved in generating configurations for implementing fault-free digital circuits on reconfigurable devices.

Genetic Algorithms (GAs) [17] are guided trial-and-error search techniques. They use the principles of Darwinian evolution which target the survival of the fittest. This is essentially done by casting a net over the entire solution space to find high fitness regions. The reprogrammability of FPGAs provides an efficient platform highly suitable for evolutionary fault refurbishment platforms [18]. In the event of faults in FPGAs, a GA can be used to search and implement alternate configurations that circumvent the faulty resource, thus providing device refurbishment.

Evolutionary approaches such as Genetic Algorithms (GAs) appear throughout the literature as a means to realize design and repair strategies on hardware-in-the-loop FPGA-based digital systems [16-18]. GAs realize search strategies based on the Darwinian evolution principles by performing genetic operations such as mutation and crossover. Several variations of GAs were introduced to enhance the performance and speed of convergence to a solution for FPGA-based systems [19]. However, many of these realizations employ software-in-the-loop simulations rather than intrinsic implementations in the FPGA fabric. Challenges of realizing practical intrinsic evolutionary strategies include the mapping of the genotype in the GA into its corresponding phenotype on the fabric, and the limited control over process automation of

altering and downloading safe bitstreams onto the device. These issues are exacerbated when the critical portions of bitstream representation are proprietary.

Only a handful of intrinsic evolution platforms have been proposed throughout the literature. However, these platforms are still inadequate since they either support a course granularity evolution which yields a limited capability and flexibility, or they entail huge resource overhead to work-around the reconfiguration limitations. This leads to a relatively high area and power budgets which might not be tolerable in highly constrained applications such as space mission systems.

An approach that provides a fast hardware/software interface between the GA and the FPGA device via a straightforward data-structure and Application Programming Interfaces (APIs) is proposed, developed, tested, and analyzed in this dissertation. A layered design is used to perform mapping operations at the finest granularity directly on the bitstream to modify LUT configurations, and reprogram the device. This approach is tailored to be invoked from within the system upon fault occurrence to achieve autonomous fault tolerance.

## 1.3. Self-x Properties: An Organic Computing Vision

Current high-performance processing systems are increasingly complex. They frequently consist of heterogeneous processor subsystems that depend on one another in nontrivial ways, where each subsystem is itself a multi-component system with diverse capabilities. The organization of these subsystems is typically static, determined with great care at design time and optimized for a

particular mode of operation. This design strategy is appropriate for systems that will be used in relatively static circumstances and that will be accessible for repair when their components fail. However, systems that will be used in dynamic situations, or those where human intervention to reach for repairs once deployed is impractical, present a different set of challenges. In these systems, the failure of a single component or a change in the desired mode of operation may result in large-scale inefficiency or even complete system failure.

Electronic systems operating in dynamic environments, therefore, require an increased capability for fault tolerance and self-adaptation, especially as their system complexities and interdependencies continue to increase. The realization of systems that are capable of exhibiting such adaptive behaviors constitutes the vision sought by *Organic Computing* (OC) by Schmeck in [20]. The organic computing paradigm places high value on the so-called *self-x* properties, which include self-configuration, self-reorganization, and self-healing [20-23]. These objectives must be maintained in an autonomous fashion, yet sufficiently constrained to avoid undesirable emergent behaviors.

Several distinct events may necessitate a change in the configuration of a multi-component system. First, a fault may occur in an individual component, which must then be replaced, repaired, or otherwise worked around. While we hypothesize that hardware failure would be the most anticipated trigger for a configuration change, other possibilities, such as a storage device reaching its capacity or the temperature of a chip becoming dangerously high, could be handled similarly. Second, the performance level or functional requirements imposed on the system may change, due to modified mission requirements or a change in the operational environment. In

this case, the operation of the system components must be adapted to satisfy new requirements, not simply restored to a previous operational state. In either case, existing components must be reconfigured accordingly.

To decide on the appropriate actions to take in response to these events, the system must assess its performance, comprehend its own current state, and enable mechanisms by which it can be modified. The degree to which self-reorganization and self-configuration can succeed will be limited by the degree to which the system is self-aware. A self-aware system would be capable of matching available resources to mission priorities, maintaining self-awareness by continually monitoring and evaluating its own state and the state of changing requirements, and using its self-awareness to enable accurate and up-to-date reallocations of system resources to improve performance.

Increasing the self-reliance of deployed systems would dramatically increase their dependability and domains of applicability. For example, complex monitoring and recording devices able to operate autonomously for long periods of time without external repair are essential for reducing the risk involved in space missions, deep-sea missions, manned and unmanned avionic missions, and deployments to remote or difficult terrestrial areas. A military or commercial satellite that cannot recover from a hardware failure becomes orbiting space junk, or must be replaced at great financial cost and societal impact. By contrast, a sustainable, self-aware satellite would offer increased dependability and extended lifetime. Even partially self-aware solutions could have enormous practical and economic impact, realized in terms of reduced maintenance costs, longer operating life, and greater autonomy of deployed hardware systems. Thus became obvious the

need for a practical design and implementation, which realizes an organic system platform that exploits the current available technology to deliver all the awareness and flexibility sought toward achieving sufficiently high reliability, dependability, and sustainability for critical systems.

#### 1.4. Contributions of Dissertation

The primary focus of this work is enhancing the fault tolerance capability and quantifying the sustainability of digital electronic systems. This is achieved through an innovative holistic architecture that enables organic self-awareness embedded within the different system hierarchylevels. By exploiting the dynamic runtime reconfigurablity of SRAM-base FPGA technology, this approach encompasses an adaptive reconfigurable redundancy scheme augmented with enhanced intrinsic evolutionary refurbishment platform. Listed below are the dissertation's main contributions. Each innovation is discussed in details in the following chapters.

i. Novel and comprehensive sustainable organic platform for SRAM FPGA-based mission-critical systems:

A two-layered architecture that integrates autonomous, organic, self-x capable hardware elements at the chip level with a supervisory software to monitor, diagnose, and refactor components at the subsystem and system levels is proposed, modeled, simulated, prototyped, and analyzed. This platform offers system oversight and management at multiple levels within the component hierarchy combining self-diagnostic capabilities of functional elements

with supervision from autonomic supervisory layer. High-level capabilities circumvent most severe impacts on mission performance, while self-repair capabilities of functional elements autonomously correct localized immanent hardware failures.

#### ii. Innovative reconfigurable adaptive redundancy scheme:

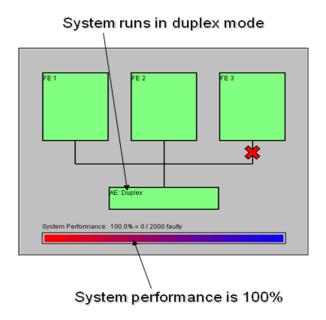

The proposed technique leverages the FPGA dynamic partial reconfiguration capability to autonomously switch between various modes of operation depending on system health at runtime. This technique optimizes chip area and power utilization over the state-of-the-art and satisfies the fault tolerance needs. Moreover, it provides an outlier-based fault identification tool which consistently achieves fault detection with one output-cycle latency for articulated faults, and eliminates the need for additional test vectors.

The fact that the system runs most of the time in duplex mode results in substantial dynamic power savings compared to the traditional widely-adopted TMR scheme. This also enhances the chip capacity to temporally accommodate more functions within unutilized fabric area while running in duplex mode. Moreover, the instantaneous switching from duplex to triplex capability provides immediate full throughput recovery upon failure while the faulty design is placed under refurbishment.

#### iii. Intrinsic GA evolutionary refurbishment integrated framework:

A GA-based hardware/software framework for intrinsic evolvable hardware is designed and evaluated for digital circuit repair using a variety of well-accepted benchmarks. Fast GA-

based autonomous refurbishment is achieved by exploiting dynamic bitstream compilation and partial reconfiguration through ultra-fast genetic operators in the micro-seconds range along with intrinsic fitness assessment on the real PFGA fabric. Three enhanced sorting genetic operators have been introduced to the digital circuit design for the first time. Consensus based evolution results in a design-independent, model-free refurbishment qualification through deterrence from dedicated pre-designed exhaustive testing cycles and reliance on discrepancy-based evaluation with actual functional stimuli.

#### iv. Expedited GA using CGT-pruned repair technique:

A novel technique that combines *Combinatorial Group Testing* (CGT)-based fault location algorithms with the Genetic algorithms to expedite the evolution convergence time is developed and analyzed. Knowledge regarding the location of hardware resource faults guides the GA search process to converge into complete repair in fewer generations than when the knowledge is unavailable. Experiments have shown that CGT-pruned genetic algorithm yields completely refurbished FPGA configurations in 37.6% fewer generations on average than a conventional GA.

#### v. Quantitative stochastic sustainability model for FPGA-based reparable systems:

A quantitative stochastic sustainability model for FPGA-based reparable systems is formulated and analyzed. This model estimates at design-time the resources required for refurbishment in order to meet mission availability and lifetime requirements in a given ecosystem of different fault types, rates, and impact. Hence, sustainability analysis provides analytical tools to refine

design appropriately within budget, area, power, and weight constraints. This model is applied to circuits from the MCNC benchmark set with variations of parameters for illustration. Moreover, the sustainability of a realistic space mission use-case is analyzed. The analysis is repeated to demonstrate how mission's sustainability and useful lifetime can be extended by exploiting FPGA resources available aboard when adopting the aforementioned developed Organic refurbishment platform.

#### CHAPTER 2: RELATED WORK

Throughout the literature, FPGA technology has been recognized as the best hardware platform available with the sufficient reconfigurability and flexibility features needed in dynamically evolving systems. Such systems are reconfigured either to achieve a refurbishment or to meet changing requirements. Similarly, FPGAs are the best candidates for practical organic computing implementations. Several fault tolerance paradigms have been explored and perhaps the most efficient and less limited ones are the evolutionary ones such as the GA based approaches.

#### 2.1. Evolution of Digital Circuit Design and Repair Tasks

Previous work on fault tolerance in FPGA-based systems varies from pre-defined design-time approaches, to completely adaptive GA-based run-time repair approaches. For example, in the pre-compiled column-based dual FPGA architecture approach [24], FPGA configurations created at design-time are utilized for error detection and fault-circumvention. These precompiled configurations have the same functional design but utilize different set of reconfigurable columns on the chip through different placement and routing constraints. Loading these configurations successively emulates shifting configurations' columns. The process continues until the column with the culprit resource is not used by the loaded configuration anymore. In this approach fault isolation is achieved by using distributed Concurrent Error Detection (CED) checkers while performing the blind reconfiguration. However, the repair process is not evolutionary and is limited by the number of available precompiled configurations. Also the solutions obtained

might lead to a high subset of resources being excluded from the operational resources as the granularity of the solutions is at the column level which is considered substantially high. Moreover, this approach scales quite poorly with multiple faults.

A traditional widely adopted fault tolerance technique is the Triple Modular Redundancy (TMR) [25]. In [16], fault tolerance is accomplished through TMR by utilizing a voting system that votes amongst three functionally-identical modules. Upon fault detection, the faulty module undergoes offline evolutionary repair without the need to perform fault isolation. Other evolutionary approaches to fault tolerance include [26] and [27], however, it is only in [28] and [29] that resource performance information is obtained, maintained and then used as feedback in the repair process. However, in [28] it is the configuration performance information that is maintained rather than the performance of the resources themselves. In [29] performance information at the resource level is maintained, however, this approach has issues such as high fault detection latency, performance degradation in the absence of fault, and increased operational complexity.

In [30], the authors present results from the adaptation of various CGT algorithms for fault isolation in FPGAs. Runtime fault detection without using special test vectors is achieved by repeatedly comparing the outputs of configurations for discrepancies as described in [31]. The presence of a faulty output ascertained using bit-wise output comparison with an ideal output provides information regarding the fitness of individual resources used by the configuration.

There are two paradigms for implementing GAs in reconfigurable applications: *Extrinsic Evolution* via functional models that abstract the physical aspects of the real device, and *Intrinsic Evolution* on the actual devices. Extrinsic approaches simplify the evolution process as they operate on software models of the FPGAs. However for applications like in-situ fault handling on deep space missions, not all fault types can be readily accommodated within software models. Additionally, abstracting the physical aspects of the target device complicates rendering the final designs into actual on-board circuits, for instance, limitations such as routability of the design cannot be ensured until the final stages of the configuration process. Furthermore, fitness evaluation on hardware usually requires less time than software simulations, and that makes intrinsic evolution mostly considered for its higher performance and scalability as an efficient approach to realizing physical designs in critical systems.

Several previous research efforts have addressed intrinsic evolution. A successful attempt on Field Programmable Transistor Array (FPTA) chips was carried out by [18]. The authors proposed new ideas for long-term hardware reliability using evolvable hardware techniques via an evolutionary design tool named EHWPack that facilitates intrinsic evolution by incorporating the PGAPack genetic engine with Labview test-bed running on UNIX workstation. They were able to intrinsically evolve a Digital XNOR Gate on two connected FPTA boards. In this dissertation, we target FPGAs rather than FPTAs and specifically the popular Xilinx Virtex family device.

Miller, Thomson, and Fogarty [17] previously addressed the importance of direct evolution on the Xilinx 6216 FPGA devices; the research explored the effect of the device physical constraints on evolving digital circuits. A mapping between the representation genotype and the device phenotype was proposed, however, no implementation details were presented. Hollingworth, Smith, and Tyrrell developed intrinsic evolution platform for a 2-bit adder on a Xilinx FPGA with partial reconfiguration to improve evolution time [32]. However, they used the JBits interface for run-time reconfiguration. JBits is Java-based, and being interpreted can face scalability and performance issues and is no longer supported.

Another way to achieve online reconfigurability is proposed by Upegui, Peña-Reyes, and Sanchez in [33]. In this approach, the system is divided into sub-modules, and several different partial reconfiguration bitstreams are generated in advance for each module using Xilinx Module Based Partial Reconfiguration flow. GA combines partial bitstreams that best perform the required task optimally or sub-optimally. This simulated approach is constrained by the limited number of possible combinations generated beforehand. Furthermore, its course granularity makes it only suitable for certain applications where the system can be divided into well-defined modules with fixed interfaces such as the neural network use case discussed by the authors.

A promising technique called the Virtual Reconfigurable Circuit (VRC) method was proposed by Sekanina in [34] and [35] and also in a similar work by Glette and Torresen [36]. This method does not change the bitstream of the FPGA itself, but rather changes the register values of a reconfigurable circuit already implemented on the FPGA, and obtains virtual reconfigurability. Although this method provides online reconfigurability, it incurs a very high area and power overhead and could increase the number of elements that can break from a fault tolerance point of view. Moreover, these schemes implement phenotype abstraction by predefining several

functions that can be performed by a computational cell. Although, this abstraction has shown benefit in convergence time in some cases [10], it incurs mapping overhead and adds constraints to the flexibility which limits the search space and does not fully exploit the hardware capability.

In several previous works [4, 37, 38], methodologies are proposed to enable runtime FPGA reconfiguration while keeping the Xilinx CAD tools out of the loop to achieve smaller reconfiguration delays. Such approaches can be used as platforms to achieving tractable intrinsic evolution.

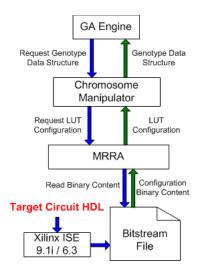

In a previous work within our research group, a Multilayer Runtime Reconfiguration Architecture (MRRA) was developed for Autonomous Runtime Partial Reconfiguration of FPGA devices [39]. The tool comprises three layers, namely Logic, Translation, and Reconfiguration layers, with well-defined interfaces for modularity and reuse. In addition, a standard set of Application Programming Interfaces (APIs) was utilized for communication with the target device. Results had shown the ability of the framework to support autonomous and dynamic reconfiguration operations. We have extended the MRRA platform to support two basic genetic operators [40] which is further extended herein to support five enhanced genetic operators namely: Single point conventional crossover, Partial Match Crossover (PMX) [41], Order Crossover (OX) [41, 42], Cycle Crossover (CX) [42, 43], and Genetic Mutation directly to realize intrinsic evolution on Xilinx Virtex-4 devices. All five genetic operators are evaluated experimentally and results are compared for their ability to achieve fault repair in a number of fault handling scenarios. This intrinsic evolution platform is used as part of the proposed solution

to achieve evolutionary refurbishment of the faulty configurations reported by the organic layer as will be discussed later in Chapter 3.

#### 2.2. Organic Computing Concepts

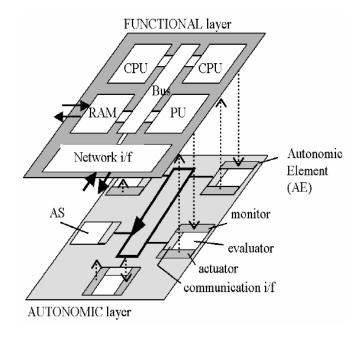

The field of organic computing is beginning to demonstrate promising results at the level of single chips. A widely known generic OC platform called the Autonomous System-on-a-Chip (ASoC) architecture, proposed in [22], is depicted in Figure 1. The ASoC platform consists of two layers: the Functional Layer and the Autonomic Layer. The ASoC Autonomic Layer contains Autonomic Elements (AEs) that are responsible for correct operation of the corresponding Functional Elements (FEs) present on the Functional Layer. Each FE (e.g., CPU, RAM, and Network Interface) has a counterpart Monitor / Evaluator / Actuator component within the Autonomic Layer.

Within the ASoC architecture, the Autonomic Layer also contains an Autonomic Supervisor (AS), which has no counterpart on the Functional Layer. The autonomic supervisor is responsible for maintaining the correct functionality of all the elements on the Autonomic Layer. The manner in which it operates is not specified by the ASoC architecture. Thus, the current proposal is largely concerned with defining the AS role and capabilities of the autonomic supervisor in more detail as comprehensive Cognitive Layer.

OC systems adhering to the ASoC architecture rely on self-organization to respond to internal imbalances and changing environmental conditions [21, 44, 45]. Reconfigurable logic devices

such as FPGAs are known to offer an attractive hardware platform for these systems, and provide the organic architecture with sufficient capability for exhibiting self-adaptive behavior [20-23]. Specifically, SRAM-based FPGA devices can realize self-adaptation within their reconfigurable logic fabric [28, 46, 47]. These approaches are capable of detecting certain types of internal errors as well as initiating reconfiguration when necessary within a single FPGA [40].

Beyond self-monitoring and self-repairing at the level of a single chip, we seek to confer these properties to the larger mission-level systems which utilize them. In order to incorporate the System-on-a-Chip autonomy into an organic-computing subsystem, system, or system-of-systems, it is necessary to monitor the functionality of the AEs within each chip, and to manage the impact of reduced chip functionality due to either permanent or transient faults while repairs are ongoing. Within the single-chip architecture, no provisions are attempted for maintaining the correctness of the AS's behavior. Finally, the self-repair process within an individual chip may be intractable due to larger than local permanent damages, so a strategy is needed for handling the impact of chip-level failures.

Within a complex system composed of many components, self-repair can take place at multiple levels. First, individual components may be able to repair themselves without changing their roles within the overall system. Second, the system may be able to restore its overall functionality by assigning new roles to different components.

Figure 1. Autonomous-System-on-a-Chip architecture [22].

The system may also be able to optimize its overall operational performance by applying both approaches concurrently. These approached can be applied within the Organic Layer.

Recent efforts in organic computing, as already discussed, address primarily the first type of recovery, in which components repair themselves in an application-independent fashion. This application-independent repair is quite appropriate for the lowest-level components of the system that perform primitive functions. The primary goal towards attaining sustainability at the component-level is refurbishment of individual components to their original functionality. When this is tractable, a single-chip repair is sufficient to recover functionality and maintain performance.

These circumstances do not apply to composites of subsystems, let alone for an entire system like a satellite containing over 100 FPGA devices dedicated to tasks ranging from signal processing to encryption. At the system level, repair strategies may be more diverse and become more closely coupled with mission requirements. Acceptable behavior may be defined by an envelope of metric values rather than a single function, and different types of suboptimal performance can be assigned different valuations depending on mission requirements. Approaches to guaranteeing correct functionality of the mission are complexly correlated with the performance of individual elements. These complexities can be addressed within the Cognitive Layer in our proposed architecture discussed in the following chapter.

In the Cognitive Layer, an application-dependent knowledge-based approach can be utilized to perform fault detection, system repair, and resource reallocation activities reliably and in a reasonable amount of time. Simultaneously, at the resource level, components ranging from sensors and actuators to processors and memory elements must individually operate within their specified tolerances to maintain acceptable performance levels.

## 2.3. Sustainability Analysis

The term sustainability is repeatedly used in ecology, economics, sociology, and environmental sciences and their interactions [48-50]. It refers to the equilibrium state of consumption versus regeneration within some open or closed system. The term Sustainability, has been applied to computer applications on a limited scale. For example, in [51], Seacord, et al. developed a sustainability model for computer software planning and management which enables the balance between the sustainment team and the customer modification requests. In [52], Watari, et al. proposed a solution to increase the sustainability of computer networks which defines the sustainability as the balance between failure events and the autonomous dynamic reconfiguration to retain connectivity. In [53], *Mocigemba* explains the transfer of the term *Sustainability* into the IT world as being the balance between economic, social and ecological interests. The term can be further studied and refined [54]. This dissertation formulates the sustainability concept into the digital electronics domain and specifically with pertinent use cases of autonomous designs deployed into error-prone unpredictable environments. In this context, Sustainability refers to the equilibrium state of failure and repair events the system undergoes while retaining functionality over mission lifetime. To the best of our knowledge, sustainability is yet to be addressed from the proposed perspective.

## 2.3.1. Need for Sustainability Analysis

Sustainability analysis in this context might be analogous to what is referred to in the literature by *reparable systems mission reliability*. Mission system reliability of reparable and non-reparable systems has been addressed in plethora of published articles in the literature. In general, the approaches can be divided into two main categories: topological or combinatorial modeling and state-space modeling.

In the combinatorial modeling, the system is mapped into a fixed structure or network. Such approaches primarily use fault trees and reliability block diagrams. Fault tree is the logical mapping of system's physical design. It depicts the relations between certain causes and basic events that lead to major failure events so called "Top events" [55-57]. There are two main approaches to calculate system reliability from fault trees: qualitative based on the *min-cut* analysis as electrical circuits have s-coherent fault trees [58, 59] and quantitative based on probabilistic evaluation [60]. In the qualitative techniques, Boolean equations are formulated for top-level failure events. Then Boolean algebra is used to calculate the exact time of failures. Alternatively, simulations can be used. On the other hand, the quantitative approaches, build the s-coherent fault tree for the design by calculating the probability of basic events based on component's failure probability density function (pdf). And then a probabilistic evaluation can be constructed for top-level events by evaluating the min-cuts of the fault tree. To reduce the complexity, the min-cuts can be approximated by calculating the upper and lower bound probabilities for top-level events.

In summary, combinatorial modeling techniques have high computational complexity that could become intractable for large systems. Furthermore, its complexity scales up exponentially with design size despite the proposed enhancements such as reduced-edges and importance sampling [61]. Additionally, these techniques are only suitable for static designs and can only address failure modes known at design time. Therefore, this class of approaches falls short with reconfigurable systems deployed in dynamic environments.

On the other hand, in the state-space modeling techniques [34, 35, 38, 62], all system states get defined based on component possible states. A component has two states: functional, or degraded. For non-reparable systems, the probability of a component going from degraded state to functional state is zero. In reparable systems a component can go back and forth between these two states with certain failure and repair probabilities. After that time, a probabilistic modeling for component state transition is formulated and accordingly a probabilistic system state transition is formulated to find the probabilities of the top-level failure events. These mainly employ Markov chains and Petri-nets.

This class of approaches works well for simple systems with few components or for large systems but at a coarse granularity as subsystem-level, i.e. failures and repairs are considered as per subsystem and no consideration is made to intra-subsystem events at the component-level. Otherwise, it may end up with a very large state space that may require lumping to become tractable such as mergeable Markov states and non-effective edge elimination [33], or splitting and simulation such as *Markov Chain Monte-Carlo MCMC* [63].

Although the aforementioned techniques from both categories tackle the problem of system reliability calculation differently, they can be all computationally intensive, fairly complex to formulate and exhibit NP-hard time complexity to resolve when applied at component granularity. Moreover, they are poorly scalable and best fit for either small systems with very limited number of components or being applied at a coarse granularity in which failures are considered at sub-system level. Real-life applications include FPGA designs with hundreds or thousands of reconfigurable resources that can span multiple chips. For example, NASA *THEMIS* mission has a reconfigurable payload called *ARTEMIS* of 3 Xilinx V4LX160 FPGA devices to perform configurable band-pass processing and *Fast Fourier Transformations* (FFT) on instrument data [64]. This represents an example of a mission critical application deployed in a very harsh environment with high number or reconfigurable resources that can be intractable to analyze using the aforementioned techniques.

The presented work aims at practically estimating the sustainability of FGPA-based reparable systems. It benefits from the particular FGPA's trait being built up from highly interconnected identical resources: Lookup Tables (LUT), Input/Output Blocks (IOB), nets, flip-flops, and MUXs". These resources have identical and statistically independent probabilistic failure distributions.

The majority of FPGA reliability calculation and enhancement related work targeted manufacturing defects or soft faults [65]. Being built from SRAM cells, FPGAs are subject to many runtime failures due to environmental and structural reasons. There are several approaches in the literature to enhance the reliability of the FPGA-based systems [66]. Few have addressed

the runtime reliability of FPGA-based systems in realistic mission use cases, and much less are those which have explored the reparable fault tolerant system's varying reliability throughout the mission lifetime. In this dissertation we introduce a concept called the sustainability of reparable fault tolerant FGPA-based systems. It provides a practical topology-agnostic stochastic method for evaluating the repair technique and the resource allocation to attain certain level of system availability for targeted mission duration.

# 2.3.2. SRAM-based Fault Modeling

FGPAs are subject to two main categories of faults: Soft and Hard faults as shown in Table 1. Soft faults are mainly Single Event Upsets (SEU) caused when a high-energy particle such as proton, neutron, alpha, or heavy ion strikes a storage element e.g. LUT, IOB, Flip-Flop, etc. This fault is manifested by a logical value inversion of that element. When the SEU occurs in the datapath flops or memories, it is transient in the sense that it only affects the data being processed at the time of the SEU and usually disappears after that. On the other hand, if the SEU impacts a configuration memory element, it causes the design to malfunction and hence called *Firm Soft Faults*. Firm soft errors can be readily recovered by reprogramming the device with the original configuration known as scrubbing [67]. Firm soft faults in the reconfiguration circuitry could disrupt any further scrubbing attempts and hence require total system re-initialization which may not be possible during mission. We call such faults *Persistent Soft Faults*. These faults are treated as permanent hard faults from reliability point of view [7].

Hard faults, on the other hand, entail permanent physical damage to the device substrate. There are three main causes of hard faults: manufacturing defects due to process imperfections known as the Infant Mortality defects, Total Ionization Dose (TID) radiation-induced and aging-induced faults [68]. Aging induced faults include: Electromigration (EM), Time-Dependent Dielectric Breakdown (TDDB), Hot Carrier Effect/Injection (HCE/HCI), and Negative Bias Thermal Instability (NBTI). EM is the phenomenon of electron depletion in very thin wires with increased temperature. This creates a highly resistive path which entails high net delays that causes the system to fail to meet timing or can result in open circuit "stuck at open" [11, 12]. TDDB is the incident when electrons are trapped in the imperfections of the oxide well enough to create a very low resistive path "short circuit" at the transistor gate terminal which results in flipping transistor state and sluggish transistor switching characteristics. TDDB rate increases at high temperatures and thin oxide layers [8-10]. HCI describes the phenomenon in which carriers gain sufficient energy to be injected into the gate oxide. The damage results in degradation in the transistor switching frequency, which can affect design frequency limit as well as functional malfunction as the path seizes to meet timing [11, 13]. NBTI occurs when holes in the PMOSFET inverted channel interact with Si compounds to produce donor type interface states and possibly positive fixed charge [11, 14].

Table 1. SRAM-Based FPGA Fault Characteristics

| Cat. | Type        | Cause               |                                                                                                                                      | Affected                     | Volatility         | Refurbish-                |

|------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------|---------------------------|

|      |             | Source              | Description                                                                                                                          | Resources                    |                    | ment                      |

| Soft | SET         | Radiation           | Soft Error Transient. Cause: SEU (high-<br>energy particle "proton, neutrons, alpha,<br>heavy ion" striking a storage element)       | Design flops<br>and memory   | Transient          | Not needed                |

|      | Firm        | Radiation           | Cause: SEU                                                                                                                           | Configuration<br>Memory*     | Semi-<br>Permanent | Scrubbing                 |

|      | PCSE        | Radiation           | Power Cycle Soft Error [69].<br>Cause: SEU                                                                                           | Reconfiguration<br>Circuitry | Persistent         | Power-on-<br>reset        |

| Hard | Manufacture | Infant<br>Mortality | Process Imperfections                                                                                                                | All                          | Permanent          | Mask out                  |

|      | TID         | Radiation           | Change switching char.                                                                                                               | LUT, IOBs,<br>MUXs, FF       | Permanent          | Avoid                     |

|      | TDDB        | Aging               | Electrons trapped in imperfections of the oxide well enough to create very low resistive path "short circuit" at the transistor gate | LUT, IOBs,<br>MUXs, FF       | Permanent          | Avoid                     |

|      | EM          | Aging               | Electron depletion in very thin wires with increased temp. creates a highly resistive path                                           | Interconnect                 | Permanent          | Avoid                     |

|      | HCI         | Aging               | Traps at oxide surface, change of VTh of transistors                                                                                 | LUT, IOBs,<br>Mem            | Permanent          | Avoid on<br>Critical Path |

|      | NBTI        | Aging               | Temperature distribution, PAR dependent                                                                                              | LUT, IOBs,<br>BRAM           | Permanent          | Avoid on<br>Critical Path |

<sup>\* 95%</sup> of memory elements including BRAM is configuration memory.

In this work, Soft faults will not be considered in our analysis due to their transient nature and straightforward resolution. Likewise, Infant Mortality faults will be disregarded too since they can be identified through exhaustive testing in design qualification and bring-up process. Radiation induced hard faults will also be ignored due to the assurance from the FPGA manufacturers through their published reliability reports [3]. For example, in [70] *Alfke et al.* indicate that XQR4000XL radiation-hardened device family exhibits latch-up immunity at LET>100 MeVcm2/mg at 125°C.

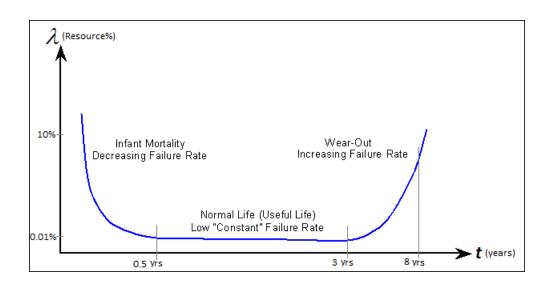

Therefore, the analysis herein will consider aging induced faults only. These faults exist and need to be address [67, 71]. This requires refurbishment techniques that involve reconfiguring the device to avoid using the broken components. Hard faults may occur during the operational phase flat region of the bath tub shown in Figure 2. However, since the use cases of interest in this research exceed the useful life we concentrate on the wear out period in the following analysis. For instance, a 90-nm SRAM-based FPGA device indicates 3-year useful life under 125°C [72] while the use case discussed in Chapter 6 has a 8-year lifetime requirement under stressful conditions. Furthermore, runtime hard faults are anticipated to become more frequent as CMOS-based devices are shrinking in size and hence reliability has become the most critical challenge facing future nanoelectronics [15].

Figure 2. The Bathtub Curve [73]

## CHAPTER 3: MULTI-LAYER HIGH-LONGEVITY ARCHITECTURE

In order to address the limitations of existing approaches, as discussed in the previous chapter, a two-layered architecture that integrates autonomous, organic, self-x capable hardware elements at the chip level with supervisory software to monitor, diagnose, and refactor components at the subsystem and system levels is proposed, developed, and evaluated. This approach makes use of the self-monitoring and self-healing properties of the individual chips, while providing an additional cognition capability for higher-level fault detection, mission-specific optimization, and adaptation to changing mission priorities.

## 3.1. System Architecture

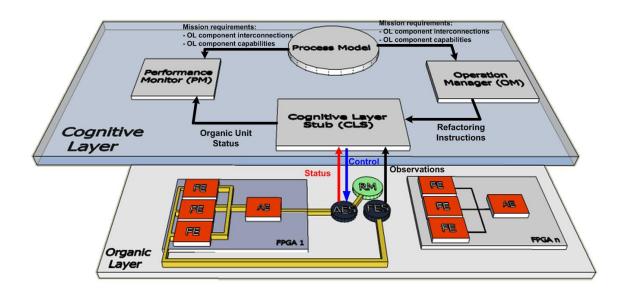

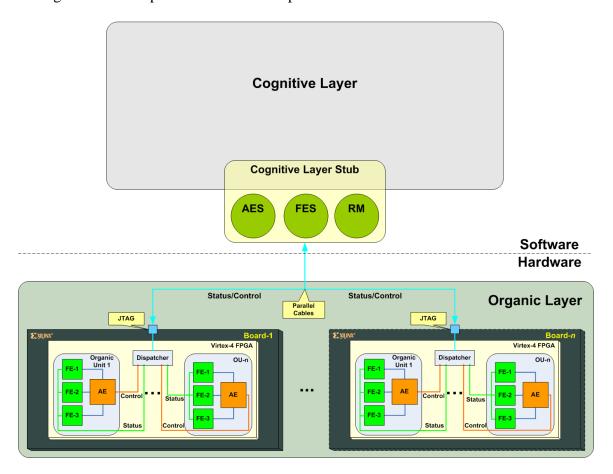

This novel architecture consists of a hardware-based organic layer and a software-based cognitive layer. Components at the organic layer are organized into overlapping functional groups, each of which bears responsibility for a particular set of mission-relevant tasks. Within the cognitive layer, monitoring and diagnostic processes continually track the behavior of these functional groups and determine whether their behavior characteristics fall within expected profiles.

As shown in Figure 3, the Cognitive Layer consists of four components: Process Model, Operation Manager (OM), Performance Monitor (PM), and Autonomic Supervisor (AS). The Organic Layer, on the other hand, consists of organic units each has one Autonomic Element (AE) and three Functional Elements (FEs) reside on the FPGA fabric. Starting in the lower left

corner of FPGA 1, two FEs process the inputs in duplicate using a Concurrent Error Detection arrangement while the third FE is a cold standby to conserve power over a Triple Modular Redundancy (TMR) [25] configuration. The functional outputs of the duplicate FEs are monitored by the AE on FPGA 1 for autonomous fault detection, isolation, resolution, and possibly self-repair using the intrinsic evolutionary repair platform discussed in the proceeding section.

Figure 3. Soar-Longevity Conceptual Architecture

Simultaneously, the same FE outputs are sent as Observations to the PM in the Cognitive Layer. The PM normalizes the FEs performance information on an absolute scale ranging from 0 to 1, and passes the normalized value to the OM. The OM detects any discrepancy between the requirements dictated by process model and the observed performance. When their difference exceeds tolerances, the OM reacts accordingly.

Thus, the Cognitive Layer interacts with the Organic Layer by:

- Managing multiple organic units on multiple FPGAs, each containing one AE, two active

FEs and one dormant FE

- Receiving status reports from AEs via the Cognitive Layer Stub (CLS).

- Determining whether output conforms to expected profiles via the PM

- When tolerances are exceeded or mission priorities change, reasoning over knowledge in the Process Model about what to do next:

- o Wait for affected FPGAs to self-repair?

- Reroute traffic to a redundant FPGA?

- o Redistribute work load across viable components?

Finally, key components of the Cognitive Layer can be implemented as an organic FPGA device to provide it with certain self-x properties.

Realization of the Soar-Longevity architecture would enhance the ability of organic computing systems to monitor system capability during execution, by incorporating a cognitive understanding of how the performance of individual components can combine to generate overall system performance. It would also improve organic computing systems' ability to manage and

configure system resources, by allowing system-level reorganization in response to component-level hardware failures. This approach combines a number of innovative aspects within an overall solution. Some of the novel features of the developed architecture are outlined in Table 2.

Table 2. Innovative aspects of the Soar-Longevity approach.

| Feature                                                                           | Innovation                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| System oversight and management at multiple levels within the component hierarchy | Combining self-diagnostic capabilities of functional elements with oversight from autonomic supervisor; high-level capabilities circumvent most severe impacts on mission performance, while self-repair capabilities of functional elements autonomously correct localized failures |  |  |

| Uniform AE design                                                                 | Pre-determined design for Autonomic Elements (AEs) despite the fact that they monitor different types of Functional Elements (FEs)                                                                                                                                                   |  |  |

| Outlier-based Fault Identification                                                | Elimination of additional test vectors while detecting first discrepant output.                                                                                                                                                                                                      |  |  |

| Model-free Refurbishment Qualification                                            | Deterrence from dedicated pre-designed exhaustive testing cycles for refurbished design qualification and reliance on discrepancy-based evaluation with actual functional stimuli.                                                                                                   |  |  |

| Intrinsic Evolutionary self-heal                                                  | Fast GA-based autonomous refurbishment with intrinsic fitness assessment on the real PFGA fabric                                                                                                                                                                                     |  |  |

Another important aspect is the orientation of the Cognitive Layer on the board outside of the critical path of execution. Consequently, while a blocking failure will remove the ability of the Cognitive Layer to provide part of the self-x capabilities to the system, the system's primary functionality and hardware-realized organic properties are not affected.

Typically, the Organic Layer should resolve any upset upon failure by itself and regain full functionality. This self-repair is performed by reconfiguring the component using pre-generated configuration bitstreams that provide comparable performance to the initially loaded configuration, or through evolutionary repair supported by the intrinsic evolution platform

proposed herein. However, depending on the scope and severity of the fault, this option may not be available. Consider the case where the board's image filtering FPGA has a logical stuck-atzero fault on the input of one of its look-up tables. The chip has detected a local failure, and has already informed the Cognitive Layer of the fault, and attempted to circumvent that failure. However, by examining the chip's performance after refurbishment and comparing it against its process model, it turns out that the new configuration is only allowing the chip to achieve 15dB SNR, which is less than the 20dB specified in the mission requirements. Here, the cognitive layer uses its knowledge of the board-level capabilities and any flexibility defined within the mission requirements to determine and implement a course of action.

The Cognitive Layer needs to know the level of impairment and the repair status of each autonomous element. Some of this information can be derived by observing functioning autonomous elements and comparing their behavior characteristics to acceptable ranges. However, since the autonomous elements gather extremely detailed data as to their functioning and use this data to produce quantitative measures of their fitness, they themselves are the best source of information as to their current capabilities. In the other direction, the autonomous elements need to be informed of reorganization requests.

The autonomous functional elements have the ability of self-monitoring through Concurrent Error Detection (CED) with Stand-by (SB) [74]. To invoke its self-healing mode, it must be able on its own to detect errors during run-time [75-77]. Reconfiguration and detection techniques explored include scrubbing, which is the continuous reconfiguration of the bitstream to refresh

the stored configuration [78], Built-In-Self-Test (BIST) techniques [79] on-chip hardware test benches [80], and Triple Modular Redundancy (TMR) [25, 74].

The information regarding the current state of the autonomous elements present within the Organic Layer is conveyed upward to the Cognitive Layer through an interface, as shown in Figure 2. To the extent that quantitative information can be made available to the Cognitive Layer, it can be used to weigh the utility of reconfiguring components against the cost of waiting for a temporarily impaired component to finish refurbishing itself. In order for this information to be transferred between the Cognitive Layer and the Organic Layer, we have designed and developed an interlayer data exchange protocol described in the following sections.

Mission priorities will be higher for some types of tasks than for others, or for some performance metrics applied to individual tasks. This will influence the allocation of resources in various ways. For instance, autonomous elements are only partially available during self-repair, so partially impaired elements may be temporarily taken off-line or reassigned by the Cognitive Layer, depending on their mission criticality. Similarly, self-repair may not completely succeed, and repaired elements may be considered less reliable than pristine elements. This will also affect the allocation of resources. The overall goal is that the system becomes self-aware at the chip level as well as the system level and thus able to respond appropriately to problems arising at all levels.

Cognitive Layer design is beyond the scope of this dissertation. The focus hereafter will be primarily on the Organic Layer design, implementation, and evaluation.

# 3.2. Organic Layer Design and Implementation